|

Главная Случайная страница Контакты | Мы поможем в написании вашей работы! | |

Умножители частоты

|

|

Удвоитель на составном каскаде. Устройство (рис. 14.18) собрано на двух транзисторах разной проводимости. В исходном состоянии оба транзистора закрыты. На входе действует сигнал гармонической формы. Положительная полярность входного сигнала открывает транзистор VT1 и закрывает транзистор VT2. Протекающий ток транзистора VT1 создает падение напряжения на резисторах R3 и R4. На первом выходе будет сигнал, совпадающий по фазе с входным сигналом, а на втором выходе сигнал будет находиться в противофазе. При равенстве сопротивлений резисторов R3 и R4 амплитуды этих сигналов будут равны. Отрицательная полуволна входного сигнала закроет транзистор VT1 и откроет транзистор VT2. На Выходе 1 появится сигнал, находящийся в противофазе с входным сигналом, а на Выходе 2 — будет совпадать по фазе с входным сигналом. Таким образом, при подаче на вход синусоидального сигнала на Выходе 1 все полуволны будут положительными, а на Выходе 2 — отрицательными. Удвоитель работает в диапазоне частот от 200 Гц до 20 кГц.

Рис. 14.18 Рис. 14.19

Транзисторный удвоитель. Удвоитель (рис. 14.19) состоит из двух транзисторов. Первый транзистор работает в схеме с коллекторно-эмиттерной нагрузкой, и коэффициент передачи его равен единице. Второй транзистор работает в схеме с ОБ. Входной сигнал создает в эмиттере VT2 ток, который на коллекторной нагрузке R3 создает напряжение, равное по амплитуде входному напряжению. Таким образом, положительная полуволна гармонического сигнала проходит через транзистор VT1 и выделяется на резисторе R3 со сдвигом по фазе 180°, а отрицательная полуволна проходит через транзистор VT2 без изменения фазы. В результате напряжение на резисторе R3 будет иметь вид, получаемый после двухполупериод-ного выпрямления входного сигнала. Удвоитель работает в широком диапазоне частот, который определяется типом примененных транзисторов.

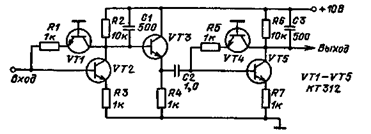

Умножитель на транзисторах. Схема удвоения частоты входного гармонического сигнала (рис. 14.20) состоит из двух каскадов. Каждый каскад увеличивает частоту сигнала в 2 раза. Положительная полуволна входного сигнала с амплитудой 0,5 В открывает транзистор VT2. Отрицательная полуволна проходит через транзистор VT1. Эти два сигнала суммируются на резисторе R2. Транзистор VT2 инвертирует входной сигнал, a VT1 — не инвертирует. На резисторе R2 формируется сигнал двухполупериодного выпрямления. Этот сигнал через эмиттерный повторитель подается на второй каскад. Амплитуда выходного сигнала повторителя равна 0,6 В.

Рис. 14.20 Рис. 14.21

Диодный умножитель. Входное гармоническое напряжение (рис. 14.21) подается на трансформатор. Во вторичной обмотке трансформатора включены две фазосдвигающие цепочки. В них происходит сдвиг фазы гармонического сигнала на 120°. В результате этого через диоды проходят сигналы, сдвинутые по фазе. На входном сопротивлении транзистора они суммируются. Третья гармоника суммарного пульсирующего сигнала выделяется контуром. Номиналы элементов фазосдвигающих цепочек рассчитаны на частоту 400 Гц.

Рис. 14.22

Удвоитель частоты. В удвоителе (рис. 14.22) применены транзисторы с одинаковыми параметрами, входящие в состав интегральной микросхемы К159НТ1. Это позволяет уменьшить паразитные составляющие больше чем на 20 дБ. Оптимальный режим удвоения получается при напряжении смещения на базах, равном 0,4 В. Удвоитель работает в широком диапазоне частот (от нижней граничной частоты пропускания трансформатора до 70 МГц) и при входном сигнале 0,5 В.

Детекторный удвоитель частоты. В основу такого удвоителя (рис. 14.23) положено двухполупериодное выпрямление на двух транзисторах VT1 и VT2. Отрицательная полуволна выходного напряжения ОУ проходит через транзистор VT1, а положительная - через транзистор VT2. Резисторы R6 и R8 выбраны одинаковыми, поэтому коэффициенты передачи обеих полуволн равны. Для устранения искажений формы выходного сигнала, вызванных влиянием порогового начального участка характеристик транзисторов, используется ОУ с нелинейной ООС. С помощью потенциометра R2 на выходе ОУ устанавливается напряжение, соответствующее минимальным искажениям выходного сигнала. Удвоитель хорошо работает при треугольной форме входного сигнала. Для этой формы входного сигнала можно последовательно включать до десяти схем умножения.

Рис. 14.23 Рис. 14.24

Рис. 14.25

Дифференциальный удвоитель. Удвоитель частоты (рис. 14.24) состоит из эмиттерного повторителя, собранного на транзисторе VT1, и усилительного каскада, построенного на транзисторе VT2. Входной сигнал через конденсатор С1 поступает в базу транзистора VT1. В эмиттере этот сигнал складывается с сигналом, который проходит через транзистор VT2. Транзистор VT2 работает в нелинейном режиме. Он пропускает отрицательные полуволны входного сигнала. Перевернутый по фазе входной сигнал будет вычитаться из сигнала эмиттерного повторителя. Уровень взаимодействующих сигналов можно регулировать резисторами R4 и R5. Резистор R4 управляет амплитудой отрицательной полуволны, а резистор R5 регулирует отношение эмиттерного сигнала к коллекторному.

Удвоитель частоты прямоугольного сигнала. Устройство (рис. 14.25, а) осуществляет преобразование входного сигнала гармонической формы в прямоугольный сигнал с удвоенной частотой. Входной сигнал поступает в эмиттеры транзисторов VT1 и VT2. Транзистор VT1 работает в режиме ограничения. Второй транзистор также ограничивает сигнал, но за счет конденсатора С1 происходит сдвиг выходного сигнала на 90° относительно входного. Два ограниченных сигнала суммируются через резисторы R6 и R7. Суммарный двухполярный сигнал с помощью транзисторов VT3 и VT4 преобразуется в сигнал с удвоенной частотой. Эпюры сигналов в различных точках показаны на рис. 14.25, б. Удвоитель работает в широком диапазоне частот от 20 Гц до 100 кГц. Такой диапазон можно перекрыть, если применить соответствующую емкость конденсатора С1. Входной сигнал должен иметь амплитуду не менее 2 В.

Компенсационный умножитель. Умножитель частоты компенсационного типа (рис. 14.26) построен на одном транзисторе. Ограниченный по амплитуде сигнал суммируется с входным сигналом гармонического вида на резисторе R1 В Deэvль тате на выходе формируется сигнал, частота которого в 3 раза вы ше частоты входного сигнала. Форма выходного сигнала не является идеально гармонической. Этот сигнал необходимо пропустить через фильтр, чтобы уменьшить уровень высоких гармоник На Форму сигнала в большой степени влияет уровень ограничения транзистора. При малых углах отсечки выходного сигнала значительно уменьшаются высокочастотные спектральные составляющие. Уменьшается при этом и амплитуда третьей гармоники.

Рис. 14.26 Рис. 14.27

Делитель на ОУ. Делитель (рис. 14.27, а) построен на четектн-ропании суммарного сигнала на выходе ОУ. На Вход 1 полается сигнал гетеродина с амплитудой 0,1 В, на Вход 2 — преобразуемый сигнал. Зависимость амплитуды выходного сигнала от преобразуемого сигнала показана на рис. 14.27, б.

Дата публикования: 2014-11-04; Прочитано: 3734 | Нарушение авторского права страницы | Мы поможем в написании вашей работы!