|

Главная Случайная страница Контакты | Мы поможем в написании вашей работы! | |

Ограничители

|

|

Ограничитель на транзисторах в схеме с ОБ. Устройство (рис. 13.1) ограничивает входной сигнал по двум уровням (±1 В). Эти уровни задаются напряжениями в базах транзисторов. Положительный: уровень устанавливается на базе транзистора VT1, а отрицательный — на базе VT2. Когда входной сигнал превышает +1 В, открывается транзистор VT1 и через эмиттерную цепь ограничивается входной сигнал. Внутреннее сопротивление этого ограничителя составляет 10 Ом.

Рис. 13.1 Рис. 13.2

Индикатор нуля. На вход индикатора (рис. 13.2) подается синусоидальный сигнал с амплитудой больше 1 В. Частота входного сигнала может иметь значения от 0 до 100 кГц. На выходе индикатора формируются отрицательные импульсы длительностью 50 мкс. Импульсы формируются в тот момент, когда входной сигнал проходит через нулевое значение. Отрицательная полуволна входного сигнала через R1 подается на эмиттер транзистора VT3 и открывает его. В это время транзистор VT2 находится в закрытом состоянии. Когда на входе существует положительная полуволна синусоидального сигнала, в открытом состоянии находится транзистор VT1. Транзистор VT2 опять будет закрыт. И только в тот момент, когда оба транзистора VT1 и VT3 закрыты, открывается транзистор VT2. Этот момент наступает при переходе входного сигнала через нулевое значение. В индикаторе можно применить интегральную микросхему К198НТ1.

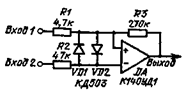

Ограничитель на ОУ. Устройство (рис. 13.3) позволяет менять уровень ограничения сигнала. На Вход 1 подается переменный сигнал, а на Вход 2 — напряжение, соответствующее уровню ограничения. При задании нулевого порога на инвертирующем входе ОУ резистор R2 можно не ставить. Максимальная амплитуда входного сигнала 3 В. Ограничитель работает на частотах не более 1 МГц.

Рис. 13.3 Рис. 13.4

Рис. 135

Однополярный ограничитель. Входной сигнал (рис. 13.4) одновременно поступает на два ОУ, но на разные по полярности входы. ПеЪвый усилитель ограничивает входной сигнал с уровня Е1, а вто-Р0и усилитель — с уровня Е2. Эти уровни можно в широких пре-Д£лах менять. В частном случае, когда £| = £2=0, ограничитель фиксирует момент перехода входного сигнала через нуль.

Двухуровневый компаратор. Приведенная на рис. 13.5, а схема включения сдвоенного компаратора позволяет выделить входной сигнал, лежащий между двумя уровнями. Эти уровни могут регулироваться в широких пределах. Если входной сигнал меньше значения ei, на выходе присутствует положительное напряжение. Аналогичное напряжение будет и при превышении входным сигналом значения £2. В промежутке между уровнями ei и £2 на выходе будет сигнал, близкий к нулевому. Аналогичную схему (рис. 13.5, б) можно построить на двух ОУ. Однако она будет значительно уступать по быстродействию интегральной микросхемы К521СА1.

Ограничитель на интегральной микросхеме К284ПУ1. В качестве усилителя в микросхеме (рис. 13.6, а) использован бескорпусный твердотельный ОУ типа К740УД1. Элементы коррекции размещены внутри интегральной микросхемы. Амплитудно-частотная характеристика усилителя приведена на рис. 136, а. Коэффициент усиления равен (1,2 — 8)104. Напряжение смещения не превышает 7,5 мВ. Разность входных токов не превышает 0,5 мкА, а входные токи — 1,5 мкА. Максимальный входной синфазный сигнал равен 8 В. Максимальный дифференциальный входной сигнал +5 В, Входное сопротивление около 50 кОм. Коэффициент ослабления синфазного входного напряжения более 65 дБ. Температурный дрейф напряжения смещения 6 мкВ/град. Температурный дрейф разности входных токов 1,5 нА/град. Скорость нарастания выходного сигнала 1 В/мкс. В микросхеме введены два стабилитрона с напряжением стабилизации 10 В. Стабилитроны включены навстречу друг другу с дифференциальным сопротивлением 220 Ом и максимально допустимым током 2 мА.

На рис. 13.6, б приведена схема двухполярного ограничителя на основе К284ПУ1. Максимальная амплитуда выходного сигнала рассчитывается по формулам

где RВ = 143 кОм; Uд = 0,7 В — прямое падение напряжения на внутреннем диоде.

На рис. 13.6, в, г показаны две схемы ограничителей входного сигнала положительной полярности, а на рис. 13.6, д, е — ограничители отрицательной полярности.

Рис. 136

Ограничитель с динамическим сопротивлением. Порог открывания первого транзистора (рис. 13.7, а) устанавливается делителем R4, R6. В эмиттер включен транзистор VT3. Когда входное напряжение превысит установленный порог, транзисторы VT1 и VT2 открываются и происходит лавинообразный процесс Коллекторный ток транзистора VT2 переводит транзистор VT3 в насыщение Пороговое напряжение уменьшается до нуля. Через базовую цепь транзистора VT1 будет протекать большой ток, который переведет транзисторы VT1 и VT2 в насыщение. При уменьшении входного напряжения транзисторы VT1 и VT2 выходят из насыщения При малых токах транзистора VT2 увеличивается напряжение на коллекторе транзистора VT1. В результате схема возвращается в исходное состояние. Переходные характеристики ограничителя приведены на рис. 13.7, б.

Ограничитель базового тока. Ограничитель (рис. 138, а) охвачен ПОС через резистор R3. За счет этого ограничитель имеет передаточную характеристику гистерезисного типа. Ширину гистере-знсной петли можно регулировать резистором R1. С увеличением сопротивления этого резистора верхняя граница петли гистерезиса увеличивается. Нижняя граница не меняется при изменении сопротивления любых резисторов. Она определяется порогом открывания транзистора VT1. Кроме того, на гистерезис влияет сопротивление резистора R4. При сопротивлении резистора R4, равном 3 кОм, меняется характер работы устройства, гистерезис исчезает. Ограничитель обладает большим коэффициентом усиления, в первую очередь определенным сопротивлением резистора R2. На рис. 13.8, б приведены переходные характеристики ограничителя.

Рис. 13.7

Ограничитель на ОУ со стабилизацией нуля. Для исключения временного и температурного дрейфа нуля ОУ в схему ограничителя (рис. 13.9) введены два транзистора. Выходные сигналы транзисторов объединяются и фильтруются с целью выделения постоянной составляющей. При подаче на вход гармонического сигнала на выходе сбалансированного ОУ должен быть прямоугольный сигнал с равными положительными и отрицательными полупериодами. На выходе фильтра при этом постоянная составляющая будет отсутствовать. При разбалансе ограничителя возникает разница в длительностях полупериодов. На выходе фильтра выделяется постоянная составляющая, которая изменяет режим ОУ. Постоянная времени фильтра выбрана так, чтобы фильтр не пропускал составляющие с частотами, кратными частоте входного сигнала. Дрейф нуля уменьшается до 10 мкВ за 1 ч. Включение корректирующих элементов ОУ можно найти в гл. 1.

Рис. 13.8 Рис. 13.9

Ограничитель высокочастотных сигналов. Ограничитель сигналов с частотами до 5 МГц (рис. 13.10, а) можно построить на микросхеме К228СА2 (рис. 13.10, б). Чувствительность схемы зависит от частоты (рис. 13.10, б). Ограничитель имеет парафазный выход. Максимальный уровень выходного напряжения не менее 2,8 В, а минимальный уровень — не более 0,4 В. Входной ток менее 40 мкА.

Рис. 13.10

Дата публикования: 2014-11-04; Прочитано: 2002 | Нарушение авторского права страницы | Мы поможем в написании вашей работы!