|

Главная Случайная страница Контакты | Мы поможем в написании вашей работы! | |

Розрахунок основних параметрів

|

|

Частота роботи процесора:  , звідси цикл виконання команди:

, звідси цикл виконання команди:  .

.

base – основа базової операції «метелик»;

N – кількість точок вхідного перетворення;

base=4;

N=256;

– кількість етапів перетворення;

– кількість етапів перетворення;

– кількість базових операцій «метелик» на одному етапі;

– кількість базових операцій «метелик» на одному етапі;

– кількість базових операцій у всьому перетворенні.

– кількість базових операцій у всьому перетворенні.

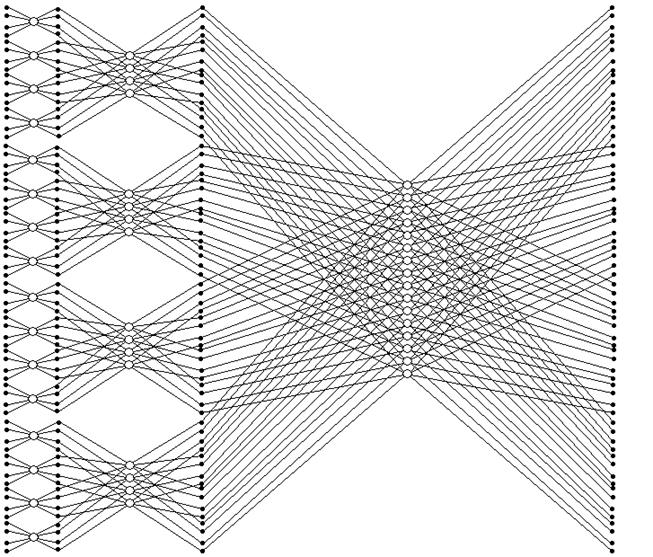

Рис.5.4. Граф 64-точкового ШПФ за основою 4 з прорідженням за часом

Рис.5.5. «Метелик» алгоритму ШПФ з прорідженням за часом

Рис.5.6 Блок-схема алгоритму 256-точкового перетворення за основою 4

Для виконання базової операції «метелик» необхідно:

v 12 операцій множення;

v 22 операцій додавання;

v 14 операцій читання з пам`яті:

- 4*2=8 (для читання дійсної та уявної частини вхідних відліків);

- 3*2=6 (для читання дійсної та уявної частини комплексних коефіцієнтів);

v 8 операцій запису:

- 4*2=8 (для запису дійсної та уявної частини вхідних відліків);

В результаті на одну базову операцію припадає 56 операцій: N на 1 мет=56 (оп)

Тривалість виконання обчислення ШПФ:

Тривалість надходження даних у процесор для обробки:

Тнадх =20нс – такт надходження даних;

Тривалість надходження даних у процесор та тривалість обчислення ШПФ:

Ця величина менша за заданий час обробки:  , тобто для виконання обчислення достатньо одного процесора.

, тобто для виконання обчислення достатньо одного процесора.

Рис.5.7. Часова діаграма роботи системи

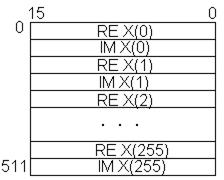

Внутрішня ОЗП процесора ADSP-21060 є 4Мбіта, тобто може бути сконфігурована наступним чином: 218 слів по 16 розрядів (4Мб=222 біт). Для розв`язання поставленої задачі необхідно 512 слів по 16 розрядів. 512х16=29х24=213. Тобто внутрішньої ОЗП цілком вистачає. Для зберігання повертаючих множників необхідно ПЗП об`ємом: 1536х16, оскільки на 1 операцію метелик необхідно 3 повертаючих множника, кожен з яких містить дійсну та уявну частину, всього є 256 базових операцій, розрядність операндів є 16. Тому 3*2*256=1536. Окремо використовуємо завантажувальну пам`ять, де буде зберігатися лістінг програми. Необхідна зовнішня ОЗП розміром 512х16 для постійного приймання даних, що надходять.

Рис.5.8.Ділянка пам`яті внутрішньої ОЗП, що приймає участь в опрацюванні

5.4. Розробка функціональної схеми

На вхід сигнального мікропроцесора надходять такі сигнали:

¨ CLKIN – сигнал синхронізації, що надходить з внутрішнього тактового резонатора;

¨  – глобальний сигнал аппаратного скиду;

– глобальний сигнал аппаратного скиду;

¨  – сигнал зовнішнього маскованого переривання;

– сигнал зовнішнього маскованого переривання;

Вихідними та двонапрямленими сигналами по відношенню до мікропроцесора є:

¨  – сигнал вибору кристалу мікросхеми завантажувальної пам`яті;

– сигнал вибору кристалу мікросхеми завантажувальної пам`яті;

¨ ADDR[31:0] – шина адреси;

¨ DATA[47:0] – шина даних;

¨  – строб читання даних з зовнішнього пристрою у мікропроцесор;

– строб читання даних з зовнішнього пристрою у мікропроцесор;

¨  – строб запису даних у зовнішній пристрій з мікропроцесора;

– строб запису даних у зовнішній пристрій з мікропроцесора;

¨  – сигнали вибору кристалів відповідно зовнішнього ПЗП(MS1) та зовнішнього ОЗП(MS0);

– сигнали вибору кристалів відповідно зовнішнього ПЗП(MS1) та зовнішнього ОЗП(MS0);

Інші сигнали або не задіяні, або їх використання не розглядається у даному прикладі.

Розробка керуючого пристрою

Призначення даного вузла – арбітраж доступу до зовнішнього ОЗП між обчислювальним процесором та давачем сигналу.

Сигнали, що надходять на керуючий пристрій:

¨ CLK – сигнал синхронізації з давача;

¨  – глобальний сигнал апаратного скиду;

– глобальний сигнал апаратного скиду;

¨ STRD – строб даних, що надходить з давача;

¨ ADDR_IN – шина адреси з обчислювального процесору;

¨  – строб читання зовнішньої пам`яті, надходить з процесору;

– строб читання зовнішньої пам`яті, надходить з процесору;

¨  – вибір кристалу зовнішньої пам`яті, надходить з процесору;

– вибір кристалу зовнішньої пам`яті, надходить з процесору;

Сигнали, що виходять з керуючого пристрою:

– дозвіл видачі даних з мікросхеми зовнішньої пам`яті;

– дозвіл видачі даних з мікросхеми зовнішньої пам`яті;

– дозвіл запису до мікросхеми зовнішньої пам`яті;

– дозвіл запису до мікросхеми зовнішньої пам`яті;

– вибір кристалу зовнішньої пам`яті;

– вибір кристалу зовнішньої пам`яті;

ADDR_OUT – шина адреси, що скеровується на мікросхему зовнішньої пам`яті;

– сигнал маскованого переривання;

– сигнал маскованого переривання;

Рис.5.9.Часова діаграма запису у зовнішній ОЗП

Регістр стану зберігає значення сигналів  ,

,  ,

,  , Вихід

, Вихід  можна використати як сигнали дозволу у буферній розв`язці для шини даних, оскільки сигнали

можна використати як сигнали дозволу у буферній розв`язці для шини даних, оскільки сигнали  та

та  взаємовиключаючі і суперечать один одному. Сигнал

взаємовиключаючі і суперечать один одному. Сигнал  можна також використати як сигнал ACK, що надходить на процесор і є підтвердженням доступу до зовнішньої пам`яті зовнішнім пристроєм.

можна також використати як сигнал ACK, що надходить на процесор і є підтвердженням доступу до зовнішньої пам`яті зовнішнім пристроєм.

Рис.5.10. Структура керуючого пристрою

Рис.5.11. Структура обчислювальної системи

Сигнал  формується лічильником при досягненні межі лічби і направляється на процесор, де обробляється програмою обробки переривань. Лічильник сам скидає сигнал переривання на початку нового циклу лічби. Лічильник сам скидається у початковий стан при надходження стробу даних, а також при подачі апаратного скиду. Дані надходять із сенсора 16-розрядними і по черзі записуються у зовнішнє ОЗП

формується лічильником при досягненні межі лічби і направляється на процесор, де обробляється програмою обробки переривань. Лічильник сам скидає сигнал переривання на початку нового циклу лічби. Лічильник сам скидається у початковий стан при надходження стробу даних, а також при подачі апаратного скиду. Дані надходять із сенсора 16-розрядними і по черзі записуються у зовнішнє ОЗП

Дата публикования: 2014-11-18; Прочитано: 976 | Нарушение авторского права страницы | Мы поможем в написании вашей работы!