|

Главная Случайная страница Контакты | Мы поможем в написании вашей работы! | |

Методы расчета показателей безотказности и безопасности

|

|

Рассмотрим методы расчета показателей для различных структур, защищенных от опасных отказов. В этих структурах для сравнения результатов обработки информации на выходах и в контрольных точках вычислительных каналов используются компараторы с несимметричной характеристикой отказов.

Вероятность безотказной работы дублированной структуры с умеренной связью (рисунок 6.1) определяется выражением [12]

, (6.1)

, (6.1)

где P 1, P & – вероятности безотказной работы соответственно канала обработки информации и выходной схемы «И»;

n – число информационных выходов модуля;

l i – интенсивность отказов элементов канала обработки информации;

l & – интенсивность отказов выходной схемы «И»;

k – число элементов канала обработки информации.

Вероятность безотказной работы мажоритарной структуры с умеренной связью (рисунок 6.2) определяется выражением [12]

, (6.2)

, (6.2)

где P 1, P мэ – вероятности безотказной работы соответственно канала обработки информации и мажоритарного элемента МЭ;

n – число информационных выходов модуля.

Рисунок 6.1 – Дублированная структура Рисунок 6.2 – Мажоритарная структура

с умеренной связью с умеренной связью

Опасным отказом в резервированном микропроцессорном модуле считается отказ, необнаруживаемый встроенными средствами контроля. Учитывая очень малое значение интенсивности опасных отказов (для высоконадежных систем l i t<<1), вероятность появления опасного отказа в дублированных и троированных модулях определяется выражениями

, (6.3)

, (6.3)

, (6.4)

, (6.4)

где tД – период диагностирования элементов модуля;

l i – интенсивность отказов канала обработки информации.

При контроле идентичности работы каналов обработки информации по выходным сигналам трудно детерминировать поведение ЭВМ при появлении отказов, поэтому все возникающие отказы считаются эквивалентными. В этом случае оценка безопасности таких модулей получается несколько заниженной.

При введении в состав дублированного микропроцессорного модуля устройства контроля совпадения сигналов на шинах внутреннего интерфейса (рисунок 6.3) показатели безотказности и безопасности определяются следующим образом [12]

, (6.5)

, (6.5)

, (6.6)

, (6.6)

где P 1, P & – вероятности безотказной работы соответственно канала обработки информации и выходной схемы «И»;

n – число информационных выходов модуля;

P УК – вероятность безотказной работы устройства контроля;

l i – интенсивность отказов элементов канала обработки информации;

k – число элементов канала обработки информации;

tД – период диагностирования элементов.

Для дублированного модуля с устройствами контроля шин и выходов (рисунок 6.4) вероятность безотказной работы равна

. (6.7)

. (6.7)

|

Вероятность появления опасного отказа в этой структуре при условии, что УК1 и УК2 безопасны, определяется выражением (6.6).

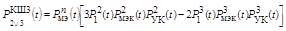

Рассмотрим методы расчета показателей безотказности и безопасности в мажоритарных структурах. На рисунке 6.5 приведена структура мажоритарного модуля с попарным сравнением сигналов внутреннего интерфейса и выходными мажоритарными элементами, отвечающими требованиям безопасности. Для этого случая показатели безотказности и безопасности определяются по формулам [12]:

, (6.8)

, (6.8)

, (6.9)

, (6.9)

где P 1, P мэ – вероятности безотказной работы соответственно канала обработки информации и выходной мажоритарной схемы;

n – число информационных выходов модуля;

P УК – вероятность безотказной работы устройства контроля;

l i – интенсивность отказов элементов канала обработки информации;

k – число элементов канала обработки информации;

tД – период диагностирования элементов.

Рисунок 6.5 – Мажоритарная структура с попарным сравнением шин

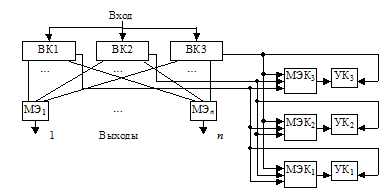

На рисунке 6.6 приведена структура микропроцессорного модуля, в котором контроль идентичности работы каналов осуществляется путем сравнения сигналов на шинах ЭВМ с истинным значением, получаемым на выходе мажоритарного элемента. В этом случае вероятность появления опасного отказа определяется выражением (6.9), а вероятность безотказной работы такого модуля – выражением:

, (6.10)

, (6.10)

где P мэк (t) – вероятность безотказной работы мажоритарного элемента контроля (МЭК) за время t.

В этом случае вероятность безотказной работы сильно зависит от надежности МЭК. Уменьшить эту зависимость можно, используя три МЭК, как показано на рисунке 6.7. В этом случае

. (6.11)

. (6.11)

Рисунок 6.6 – Мажоритарная структура с мажоритарным

элементом контроля

Рисунок 6.7 – Мажоритарная структура с резервированными

мажоритарными элементами контроля

Таким образом, по выражениям (6.1) – (6.11) можно определить вероятности безотказной работы и вероятности появления опасного отказа для основных структур микропроцессорных централизаций. Полученные вероятности можно использовать для определения остальных показателей безотказности и безопасности, используя выражения взаимосвязи показателей.

6.3 Расчет показателей безопасности и безотказности

микропроцессорных централизаций

Рассмотренные аналитические выражения для определения показателей безотказности и безопасности дублированных и мажоритарных структур могут использоваться и при расчетах более сложных структур. В этом случае для получения аналитического выражения применяется метод расчета, основанный на расчетно-логических схемах.

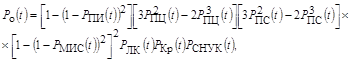

В качестве примера рассмотрим расчетно-логическую схему для определения показателей безотказности микропроцессорной централизации SSI (рисунок 6.8), где в качестве элементов схемы использованы: процессор интерфейса (ПИ), процессор централизации (ПЦ), процессор связи центральной подсистемы (ПС), модуль информационной связи (МИС), локальный компьютер (ЛК), компаратор, управляющий напольным устройством (Кр), схемы непосредственного управления объектами (СНУК).

Рисунок 6.8 – Расчетно-логическая схема для определения показателей

безотказности

В системе произведено мажоритарное резервирование ПЦ и ПС. Резервирование ПИ и МИС произведено по схеме постоянно включенного и нагруженного резерва. Из расчетно-логической схемы следует, что вероятность безотказной работы данной системы микропроцессорной централизации

(6.12)

где Р ПИ, Р ПЦ, Р ПС, Р МИС, Р ЛК, Р Кр, Р СНУК – вероятности безотказной работы соответственно ПИ, ПЦ, ПС, МИС, ЛК, Кр, СНУК.

Для расчета показателей безопасности составляется расчетно-логическая схема, учитывающая только элементы, отказ которых может привести к опасному отказу системы в целом. Так как ПИ не влияет на безопасность системы, то его из расчетно-логической схемы можно исключить. Расчетно-логическая схема для определения показателей безопасности микропроцессорной централизации SSI приведена на рисунке 6.9.

Рисунок 6.9 – Расчетно-логическая схема для определения показателей

безопасности

Вероятность опасных отказов данной системы для случая l t <<1 можно определить из следующего выражения:

, (6.13)

, (6.13)

где Q ПЦ, Q ПС, Q МИС, Q ЛК, Q Кр, Q СНУК – вероятности опасного отказа соответственно ПИ, ПЦ, ПС, МИС, ЛК, Кр, СНУК.

|  | ||

На основании приведенных формул может быть произведен расчет времени наработки на отказ и наработки на опасный отказ системы микропроцессорной централизации или других показателей безопасности и безотказности.

7 внедрение микропроцессорных систем железнодорожной автоматики

на железных дорогах мира

За последние 25 лет СЖАТ, построенные на базе микропроцессорной техники, постепенно вошли в железнодорожную практику. Их производством занимаются многие известные фирмы, а внедрение происходит не только в развитых, но и в развивающихся странах на участках, необорудованных СЖАТ, и на строящихся линиях.

Специалисты считают, что традиционные системы сигнализации, централизации и блокировки (СЦБ) обладают хорошей долговечностью (до 80 лет жизни) [1]. Поэтому темпы внедрения новых систем на железных дорогах обычно невысоки. К тому же эти темпы сдерживаются трудностями в решении проблемы безопасности микропроцессорных систем. В связи с этим на железных дорогах мира находится в эксплуатации много устройств и систем СЦБ разных поколений и модификаций. Например, в Швейцарии в настоящее время работают 163 механических, 260 электромеханических, 413 релейных и только одна микропроцессорная централизация стрелок и сигналов. Аналогично обстоит дело и во многих других странах.

В то же время существует устойчивая тенденция к разработке и внедрению микропроцессорных СЖАТ взамен выработавших свой ресурс старых систем. Переход на новую элементную базу обусловлен резко возросшими объемами работы и увеличением скорости обмена как управляющей, так и известительной информацией. Отдельные посты централизации охватывают участки до 250 км, на которых одновременно находятся сотни поездов, многие из которых движутся со скоростью свыше 250 км/ч [13].

Основные тенденции внедрения микропроцессорных СЖАТ рассмотрим на примере микропроцессорных систем централизации стрелок и сигналов.

Первая из систем нового поколения – микропроцессорная централизация (МЦ) IZS-750 – была разработана шведской фирмой ABB Signal и внедрена на станции Гетеборг в 1978 г. Последующие системы этой фирмы (например, Ebiloc 850), а также системы других скандинавских фирм (например, система IZSD 770 датской фирмы DZI) базируются на одноканальной структуре с двумя диверситетными программами. Они работают в односекундном системном цикле с тестовым периодическим контролем. Для повышения надежности системы на больших станциях применяют второй компьютер в режиме горячего резерва. В настоящее время на железных дорогах Швеции, Дании, Норвегии, Финляндии, Испании, Болгарии и Польши работают более 100 централизаций данного типа.

Первая британская микропроцессорная централизация SSI (Solid State Interlocking) разработана фирмой GEC/GB и работает на станции Лимингстон Спа с 1985 г. Она построена по принципу однопрограммной многоканальной системы «два из трех» и функционирует в циклическом режиме с периодом 0,85 с. Связь с напольными объектами осуществляется модулями со структурой «два из двух». Аппаратные средства контроля подвергаются непрерывному тестированию. Структура системы допускает реконфигурацию при отказах. На разных станциях мира эксплуатируют более 20 подобных централизаций.

Фирмами Westinghouse (Великобритания), Safetran (США) и Dimetronic (Испания) разработана система микропроцессорной централизации Westrace, предназначенная для протяженных участков с раздельными пунктами малых размеров. Westrace – это система с одноканальным техническим и диверситетным программным обеспечением. Причем диверситетность программного обеспечения достигается различными методами компиляции одной и той же программы. Результаты работы программ сравниваются программным способом. Централизации этого типа внедрены на линиях местных перевозок в Австралии и Испании.

В разработке и производстве нового поколения систем в Германии принимают участие известные фирмы Siemens, AEG и Alcatel SEL. В 1983 году было принято решение об опытной эксплуатации систем микропроцессорной централизации, разработанных фирмами Alcatel SEL, Siemens и AEG.

Все три системы являются мультипроцессорными системами с тремя функциональными уровнями. Верхний уровень представлен ЭВМ, которые управляют вводом и отображением данных. ЭВМ среднего уровня (районные ЭВМ) реализуют сигнальные зависимости, обеспечивая формирование, замыкание и размыкание маршрутов, проверку допустимости воздействий на отдельные напольные устройства и т. д. Каждая ЭВМ этого уровня обслуживает определенный район станции. ЭВМ нижнего уровня непосредственно управляют напольными устройствами.

Базовая концепция фирмы Siemens получила название SIMIS. В ней используются два независимых вычислительных канала, которые работают синхронно и синфазно по одной программе с аппаратным сравнением по принципу «два из двух». Команды, вырабатываемые в каждом канале, сравниваются двумя независимыми компараторами. Решения принимаются к исполнению только в тех случаях, когда сигналы на выходах обоих компараторов идентичны. В системе имеются тестовые программы, которые проверяют исправность вычислительных каналов в промежутках между обработкой оперативной информации. Безошибочность программного обеспечения достигается комплексными методами разработки и верификации.

Наряду с работой в режиме «два из двух» в особо ответственных ситуациях используются трехканальные безопасные структуры «два из трех», позволяющие повысить эксплуатационную готовность системы.

Вычислительные средства SIMIS имеют модульное построение. Это позволяет быстро формировать из них ту вычислительную структуру, которая соответствует конкретному объему решаемых задач и уровню требуемой надежности. Обмен информацией между компьютерами SIMIS осуществляется через двухканальную линию связи. В случае неисправности одного канала производится автоматическое переключение на одноканальный режим.

Существуют различные модификации систем, отличающиеся количеством управляемых объектов и требованиями безопасности. Система EI S предназначена для управления крупными станциями, EI S Regio – для малых станций, управляемых из единого центра, SICAS – для второстепенных участков и заводских путей.

В апреле 1989 года введена в эксплуатацию система микропроцессорной централизации на станции Кьяссо (Швейцария). В зону действия поста МЦ на станции Кьяссо входят 174 стрелки, 354 основных, маневровых и дополнительных сигнала, семь устройств путевой блокировки и 300 рельсовых цепей. До внедрения МЦ для управления перевозочным процессом на этой станции использовались один распорядительный и 4 исполнительных поста ЭЦ. МЦ базируется на микропроцессорных блоках компактного исполнения SIMIS-C. Всего в основном и двух вспомогательных зданиях поста МЦ установлено 69 ЭВМ.

Система микропроцессорной централизации EI S, установленная на станции Ганновер, осуществляет контроль и управление более чем 900 исполнительными устройствами.

Система EI S Regio предполагает автоматическое управление стрелками и сигналами участка железной дороги с общего поста диспетчерской централизации. В основу EI S Regio положен принцип минимального количества аппаратуры, обеспечивающей автоматическое управление движением поездов на станциях с минимальным путевым развитием. В состав минимального модуля напольной аппаратуры EI S Regio входят четыре главных сигнала, путевые датчики Indusi, два предупредительных сигнала, два стрелочных перевода с электроприводом, напольная аппаратура счета осей, устройство запирания ключей от стрелочных замков. Этот минимальный модуль можно наращивать дополнительными элементами в зависимости от топологии станции.

Унифицированы также станционные модули, в которых устанавливается постовая аппаратура EI S Regio. Из станционного модуля можно управлять напольными устройствами, находящимися на удалении до 13 км.

Система SICAS (Siemens Computer Aided Signalling) предназначена для применения на региональных участках железных дорог, заводских путях, железнодорожных переездах, грузовых дворах. Это гибкая система централизации, удовлетворяющая менее высоким требованиям по безопасности и допускающая дальнейшее расширение путем добавления новых модулей. Предусмотрены исполнения системы SICAS с двумя или тремя вычислительными каналами. На уровне управления используются стандартные персональные ЭВМ, на базе которых строятся автоматизированные рабочие места (АРМ). Наличие стандартных компонентов и модульное построение позволяют минимизировать время проектирования системы и сократить затраты на разработку. Всего фирмой Siemens установлено более 100 различных типов микропроцессорных централизаций на железных дорогах Германии, Австрии и Швейцарии.

Микропроцессорная централизация типа EIA, разработанная фирмой AEG и находящаяся в эксплуатации на станции Дибург с 1988 г., также использует принцип многоканальной обработки информации. В МЦ фирмы AEG все ЭВМ, используемые для обработки ответственной информации, построены на базе универсальной микропроцессорной системы с безопасными отказами LOGISIRE C. Эта система состоит из двух идентичных вычислительных каналов, в которые загружено одинаковое программное обеспечение. Каналы работают независимо друг от друга. Безопасность функционирования обеспечивают специальная операционная система и защищенное от опасных отказов устройство контроля и отключения.

Микропроцессорная централизация EI L фирмы Alcatel SEL базируется на стандартных ЭВМ, на которых построены модули обеспечения безопасности SELMIS. Они имеют в своем составе контуры безопасности, являющиеся совокупностью аппаратных и программных средств. Принципы построения контуров безопасности позволяют использовать для выполнения ответственных команд стандартные ЭВМ, обладающие большой вычислительной мощностью.

Безопасность блоков SELMIS основана на многократной обработке информации в независимых параллельно работающих вычислительных каналах с последующим сравнением в этих же каналах входных, контрольных, промежуточных и выходных данных с помощью программных средств. Для достижения высокой эксплуатационной готовности применяется преимущественно схема «два из трех».

Одним из перспективных направлений считается создание децентрализованных микропроцессорных систем управления. В Германии разработана децентрализованная система управления MCDS, построенная на базе устройства местного микропроцессорного управления стрелкой типа IVV-MCEOW-2M, дополненного устройствами управления светофором типа IVV-MCSIG-2M и контроля свободности пути типа IVV-MCGFE2M.

Децентрализованная ЭВМ может управлять группой из 32 устройств управления стрелками, 50 устройств контроля свободности пути и 50 сигналов. В систему MCDS можно объединить до 10 таких ЭВМ. Информацию, поступающую от децентрализованных ЭВМ и вводимую диспетчером, обрабатывает центральная ЭВМ. Текущая эксплуатационная ситуация отображается на экране цветного дисплея.

Центральная ЭВМ передает задания на установку маршрутов децентрализованным ЭВМ и выводит извещения о состоянии напольных устройств. Для ввода заданий служит клавиатура. Установку маршрутов осуществляют децентрализованные ЭВМ, в ПО которых реализованы все маршрутные зависимости.

Система микропроцессорной централизации Elektra, созданная фирмой Alcatel Austria совместно с Австрийским исследовательским центром в Зайберсдорфе, содержит два одинаковых в аппаратном отношении канала с различным программным обеспечением. Первый канал решает функциональные задачи и реализует логические зависимости при установке маршрутов. Второй канал осуществляет контроль безопасности. Программное обеспечение устройств логического канала составлено на языке программирования высокого уровня CHILL. Канал безопасности работает с экспертной системой PAMELA, в которой использован одноименный язык программирования, разработанный в исследовательском центре фирмы Alcatel. Экспертная система методами искусственного интеллекта на базе заложенных в нее знаний дежурного по станции и технологических инструкций осуществляет контроль правильности работы первого канала. Первая система МЦ Elektra была установлена в 1989 г. на станции Ноймарк-Кальхам Австрийских железных дорог.

Французская система МЦ разработана фирмой Alsthom. Система построена по модульному принципу, что позволяет учитывать специфику конкретной станции путем ввода соответствующих параметров в ПО каждого модуля. Для передачи информации между модулями служит кольцевая сеть. Разработка ПО МЦ ведется с помощью языка программирования высокого уровня Ada.

Американская фирма General Railway Signal (GRS) с начала 80-х годов разрабатывает и производит системы МЦ VPI с одноканальным техническим обеспечением. В стандартном исполнении система VPI может управлять 320 безопасными входами и выходами. Возможно объединение нескольких таких модулей для управления крупными станциями, такими как Нью-Йорк-Центральный, на которой работают совместно 17 систем VPI.

Безопасность при одноканальном техническом обеспечении в системе VPI достигается за счет того, что в центральной ЭВМ циклически одна за другой обрабатываются программа первичной логики и программа логики обеспечения безопасности. Программа первичной логики работает с дублированными данными, которые размещены в разных областях памяти. Обработка обоих массивов данных осуществляется последовательно одним и тем же программным обеспечением.

Главный цикл, реализующий логику централизации, имеет длительность 1 с. Он прерывается каждые 50 мс циклом обеспечения безопасности, в течение которого все включенные безопасные выходы проверяются на допустимость их включения в соответствии с массивами данных центральной ЭВМ. При обнаружении нарушения не позднее чем через 150 мс специальное реле размыкает цепь питания соответствующего модуля ввода-вывода.

Система достаточно широко эксплуатируется в США, Нидерландах, Испании, Италии, Австралии и странах Азии.

На железных дорогах Японии разработана и внедряется система МЦ SMILE. В нее заложена трехканальная структура с переменным порогом мажорирования, обеспечивающая высокий уровень эксплуатационной готовности. Процессоры работают синхронно от общего генератора тактов. Аппаратный компаратор с самоконтролем сравнивает потенциалы на внутренних магистралях попарно. Периодический контроль осуществляется с помощью программного счетчика. Для небольших станций применяется модификация mSMILE, двухканальная, с аппаратным самопроверяемым компаратором и горячим резервом. Первая система SMILE введена в постоянную эксплуатацию на станции Хигаси-Каганава в марте 1985г.

|  | ||

В литературе имеются сведения и о других современных микропроцессорных системах железнодорожной автоматики. В них используются принципы обеспечения безопасности, рассмотренные в данном пособии. Безотказность достигается использованием многоканальных систем. Обычно применяется трехканальное мажорирование или ненагруженный горячий (холодный) резерв. Безопасность достигается сравнением работы каналов с помощью самопроверяемых компараторов. Обеспечение безопасности однопрограммных систем возможно путем достижения безошибочности, а многопрограммных систем – усилением степени диверситета.

СПИСОК литературЫ

1 Методы построения безопасных микроэлектронных систем железнодорожной автоматики / В.В. Сапожников, Вл. В. Сапожников, Х.А. Христов, Д.В. Гавзов; Под ред. Вл. В. Сапожникова. – М.: Транспорт, 1995. – 272 с.

2 РТМ 32 ЦШ 1115842.01-94. Безопасность железнодорожной автоматики и телемеханики. Методы и принципы обеспечения безопасности микроэлектронных СЖАТ. – СПб.: ПГУ ПС, 1994. – 120 с.

3 Балашов Е.П., Пузанков Д.В. Проектирование информационно-управляющих систем. – М.: Радио и связь, 1987. – 255 с.

4 Внедрение систем МЦ на железных дорогах Австрии // Железные дороги мира. – 1990. – №3. – С. 27–29.

5 Система микропроцессорной централизации фирмы AEG // Железные дороги мира. – 1990. – №5. – С.39–42.

6 Linde H., Schiweck L. W. Der Sichrheitsnach weis auf Bauelementenebene// Signal und Draht, 1981. – №9. – С. 17–21.

7 Майерс Г. Надежность программного обеспечения. – М.: Мир, 1980. –360 с.

8 Липаев В.В. Тестирование программ. – М.: Радио и связь, 1986. – 296 с.

9 Сертификация и доказательство безопасности систем железнодорожной автоматики / В.В. Сапожников, Вл. В. Сапожников, В. И. Талалаев и др.; Под ред. Вл. В. Сапожникова. – М.: Транспорт, 1997. – 288 с.

10 Харлап С. Н., Кочуров Д. С. Надежные программные реализации управляющих алгоритмов: Учебно-методическое пособие по подготовке к лабораторным работам по дисциплинам “Программно-математическое обеспечение микропроцессорных систем” и “Микропроцессорные информационно-управляющие системы на транспорте. – Гомель: БелГУТ, 1999. – 56 с.

11 Микропроцессоры: В 3 кн. Кн. 2. Средства сопряжения. Контролирующие и информационно-управляющие системы: Учебник для техн. вузов/ Под ред. Л.Н. Преснухина. – Мн.: Выш. шк., 1987. – 303 с.

12 РТМ 32 ЦШ 1115482.02-94. Безопасность железнодорожной автоматики и телемеханики. Методы расчета показателей безотказности и безопасности СЖАТ. – СПб.: ПГУ ПС, 1994. – 36 с.

13 Современные зарубежные системы микропроцессорной централизации (МПЦ) // Автоматика, связь, информатика – 2000. – №7. – С. 45–47.

14

|

Станционные системы автоматики и телемеханики: Учебник для вузов ж.-д. трансп. / Вл. В. Сапожников, Б.Н. Елкин, И.М. Кокурин и др.; Под ред. Вл. В. Сапожникова. – М.: Транспорт, 1997. – 432 с.

Содержание

Введение................................................................................................................................. 3

1 Основные принципы построения систем обеспечения безопасности.............................. 5

1.1 Концепция и стратегии обеспечения безопасности.................................................... 5

1.2 Иерархия уровней обеспечения безопасности.......................................................... 10

2 Структурные методы обеспечения безопасности в микропроцессорных системах железнодорожной автоматики 13

2.1 Структуры безопасных МИУС................................................................................. 13

2.1.1 Одноканальная система с одной программой и средствами внутреннего контроля и самотестирования 13

2.1.2 Одноканальная система с диверситетными программами................................ 15

2.1.3 Дублированная система со слабыми связями.................................................... 16

2.1.4 Дублированная система с умеренными связями............................................... 17

2.1.5 Дублированная система с сильными связями................................................... 19

2.1.6 Дублированная система с сильными связями и внешним тестированием..... 20

2.1.7 Самопроверяемая дублированная система........................................................ 22

2.1.8 Мажоритарная система с умеренными связями................................................ 23

2.1.9 Мажоритарная система с сильными связями.................................................... 25

2.1.10 Мажоритарная система с сильными связями и внешним тестированием.... 26

2.2 Реализация безопасных схем внутреннего контроля и сравнения.......................... 28

2.2.1 Принципы построения безопасных схем внутреннего контроля...................... 28

2.2.2 Реализация безопасных схем внутреннего контроля в одноканальной структуре 31

2.2.3 Реализация безопасных схем сравнения в многоканальных структурах......... 34

3 Безопасные логические элементы................................................................................... 40

3.1 Принципы построения безопасных логических элементов..................................... 40

3.2 Декодеры сигналов логических переменных........................................................... 42

3.3 Импульсные схемы с внешним тактированием....................................................... 45

3.4 Автогенераторные логические элементы................................................................. 48

3.5 Самопроверяемые логические элементы................................................................. 50

4 Организация безопасного интерфейса с объектом управления................................... 52

4.1 Требования к специализированным УСО................................................................ 52

4.2 Устройства включения исполнительных реле......................................................... 53

4.3 Безопасный ввод информации................................................................................... 56

5 Программные методы обеспечения безопасности......................................................... 58

5.1 Структура программного обеспечения микропроцессорной централизации........ 58

5.2 Основные принципы обеспечения безопасности программного обеспечения...... 60

5.3 Обнаружение искажения вычислительного процесса.............................................. 62

5.3.1 Обнаружение программных ошибок.................................................................. 62

5.3.2 Обнаружение отказов и сбоев аппаратных средств........................................... 64

5.3.3 Самопроверяемые программы........................................................................... 64

5.3.4 N -версионное программирование....................................................................... 66

5.4 Исправление ошибок и устойчивость к ошибкам.................................................... 66

6 Порядок расчета показателей безотказности и безопасности МИУС......................... 69

6.1 Основные показатели безотказности и безопасности.............................................. 69

6.2 Методы расчета показателей безотказности и безопасности................................... 70

6.3 Расчет показателей безопасности и безотказности микропроцессорных централизаций 75

7 Внедрение микропроцессорных систем железнодорожной автоматики на железных дорогах мира 77

Список литературы.............................................................................................................. 83

Учебное издание

БОЧКОВ Константин Афанасьевич,

ХАРЛАП Сергей Николаевич

Дата публикования: 2014-11-02; Прочитано: 2208 | Нарушение авторского права страницы | Мы поможем в написании вашей работы!