|

Главная Случайная страница Контакты | Мы поможем в написании вашей работы! | |

Реализация безопасных схем сравнения в многоканальных структурах

|

|

Безопасные схемы сравнения в многоканальных структурах МИУС выполняют сравнение соответствующих сигналов на шинах (в памяти) каналов между собой. На рисунке 2.14 приведена обобщенная структура дублированного микропроцессорного модуля. Шины внутреннего интерфейса контролируются безопасной схемой сравнения с несимметричной характеристикой отказов (БСС1).

Рисунок 2.14 – Обобщенная структура дублированного

микропроцессорного модуля

Выходная информация на внешнем интерфейсе формируется схемой сравнения БСС2, контролирующей идентичность состояния выходов обеих ЭВМ.

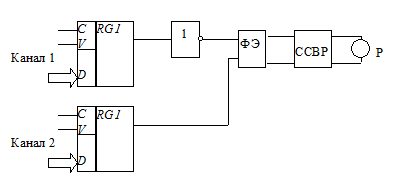

Для реализации безопасных схем сравнения можно воспользоваться свойствами самопроверяемых тестеров для равновесных кодов. Пример функциональной схемы устройства сравнения шин дублированной системы приведен на рисунке 2.15.

Рисунок 2.15 – Функциональная схема устройства сравнения шин

дублированной системы

Сигналы от второго микропроцессора поступают на устройство сравнения в инверсном виде. На каждый 2/4-СПТ поступают по два соответствующих сигнала с каждого канала. Таким образом формируется равновесный код.

При нарушении согласованной работы микропроцессоров обоих каналов на выходах контрольной схемы появляется непарафазный сигнал, который регистрируется фиксирующим элементом (ФЭ). Структура ФЭ аналогична представленной на рисунке 2.12.

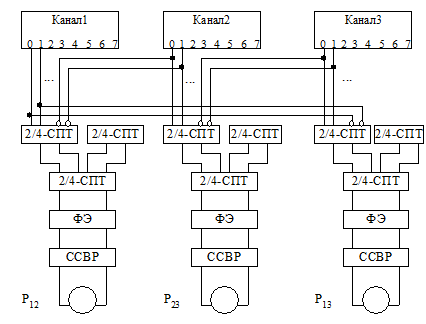

Устройство контроля шин трехканальной структуры может быть также выполнено на основе самопроверяемых тестеров (рисунок 2.16). Сигналы на шинах микропроцессоров попарно сравниваются, так же как и в дублированной структуре, с помощью тестеров 2/4-СПТ.

Рисунок 2.16 – Устройство контроля шин трехканальной структуры

При отказе одного из микропроцессоров выключаются два из трех контрольных реле. Например, при отказе первого канала отключатся реле Р12 и Р13, т. к. реле Р12 контролирует синхронную работу первого и второго каналов, а реле Р13 – первого и третьего каналов. С помощью контактов контрольных реле осуществляется дешифрация номера неисправного канала и его отключение (рисунок 2.17).

Рисунок 2.17 – Схема дешифрации номера неисправного канала

Выключение двух контрольных реле влечет за собой выключение одного из питающих реле, которое своими контактами отключает питание неисправного канала. Система при этом деградирует до двухканальной системы, сохраняя свою работоспособность. При восстановлении неисправного канала, он может быть включен в работу только при участии человека. Момент включения восстановленного канала должен быть синхронизирован с работой остальных каналов.

Если до восстановления неисправного канала произойдет еще один отказ, то произойдет рассогласование работы двух оставшихся каналов. Это приведет к выключению последнего контрольного реле, которое выключит оба оставшихся питающих реле. Все три канала будут выключены и система перейдет в защитное состояние.

Сократить число элементов и значительно повысить надежность устройства контроля микропроцессорных модулей можно за счет сравнения кодовых последовательностей на шинах не в параллельном виде, а в последовательном. С этой целью для мультиплексирования сигналов на шинах микропроцессора можно использовать универсальные сдвиговые регистры (рисунок 2.18).

Рисунок 2.18 – Последовательное устройство контроля дублированной структуры

В один и тот же момент времени производится запись информации с шин вычислительных каналов в соответствующие сдвиговые регистры. Затем по импульсам с тактового генератора производится поразрядное сравнение данных в обоих регистрах. При обнаружении рассогласования данных блокируется ФЭ и выключается питающее реле.

Структурная схема устройства контроля шин мажоритарно-резервированных микропроцессорных моделей приведена на рисунке 2.19. В данном случае сигналы каждого канала сравниваются с выходом мажоритарного элемента «2 из 3». Сигнал на выходе мажоритарного элемента определяется большинством входных сигналов. В устройстве контроля не требуется дешифратор неисправного канала, т. к. контрольное реле подключено к соответствующему каналу обработки информации. Поэтому, при отказе вычислительного канала, выключается соответствующее реле.

Рисунок 2.19 – Последовательное устройство контроля мажоритарной

структуры

Для повышения отказоустойчивости устройства контроля мажоритарный элемент может быть выполнен резервированным, как это показано на рисунке 2.20.

Последовательные устройства контроля для обеспечения высокой достоверности должны выполнять операции сравнения сигналов в течение одного такта (одной команды) работы микропроцессора в зависимости от степени синхронизации каналов.

Рисунок 2.20 – Последовательное устройство контроля мажоритарной

структуры с резервированным мажоритарным элементом

|

Таким образом, во второй главе рассмотрены основные структуры безопасных микропроцессорных систем, их достоинства и недостатки. Приведены типовые решения по организации аппаратного контроля и способам локализации отказов в этих структурах. В следующей главе рассмотрим принципы построения безопасных логических элементов, использующихся на аппаратном уровне защиты для создания контрольных элементов МИУС.

Дата публикования: 2014-11-02; Прочитано: 1045 | Нарушение авторского права страницы | Мы поможем в написании вашей работы!