|

Главная Случайная страница Контакты | Мы поможем в написании вашей работы! | |

Рмс. 15.36

|

|

Рис. 15.37 Рис. 15.38

Рис. 15.39

Рис. 15.40

Рис. 15.41

Сбрасываемый интегратор. Сброс интегратора (рис. 1541, а) осуществляется при поступлении на управляющий вход положительного импульса. Первый транзистор работает в нормальном режиме. При напряжении на интегрирующем конденсаторе больше 0,7 В транзистор VII обладает достаточным коэффициентом передачи тока и шунтирует значительный ток. При напряжении на конденсаторе меньше 0,7 В коэффициент передачи транзистора падает. Для уменьшения остаточного напряжения на конденсаторе исполь зуется инверсное включение транзистора VT2. В этом случае неподобранные транзисторы дают около 20 мВ. На рис. 1541, б приведена зависимость остаточного напряжения от управляющего

Рис. 15.42

Интегратор на ОУ со сбросом на транзисторах. Интегратор (рис. 15 42, а, б) построен на ОУ, в цепь ООС которого включен конденсатор. Для разряда конденсатора в схему введены два транзистора, которые находятся в закрытом состоянии. С приходом управляющего напряжения положительной полярности один из транзисторов открывается. При любой полярности выходного сигнала ОУ транзисторп работают в нормальном режиме. Через этот транзистор протекает основной ток разряда конденсатора. Инверсное включение транзистора уменьшает остаточное напряжение на конденсаторе. Зависимость остаточного напряжения от управляющего сигнала показана на рис. 15 42, в. Время разряда конденсатора с б В до 10 мВ составляет меньше 1 икс.

Рис. 15.43

Интегратор с разрядным полевым транзистором. В качестве разрядного ключа в сбрасываемом интеграторе (рис. 15.43, а) применен полевой транзистор. В нормальном состоянии он закрыт. С приходом управляющего сигнала транзистор открывается и входит в насыщение. В зависимости от амплитуды управляющего сигнала остаточное напряжение может менять знак. Это связано с тем, что часть управляющего напряжения проходит через открытые n -р переходы полевого транзистора. На графиках рис. 15.43, б, в приведены характеристики интегратора.

Рис. 15.44

Увеличение постоянной времени RС--цепи. Для сравнительно небольших номиналов цепочки RC устройство (рис. 15.44) позволяет получить большие постоянные времени интегрирования. Постоянная времени цепочки R3, С увеличивается в 104 раз. Выходные сигналы ОУ являются противофазными. Дрейф и уровень шума определяются- так же, как для усилителя с замкнутой ОС. Поскольку коэффициент усиления интегральной микросхемы DA2 равен единице, то общее усиление определяется коэффициентом усиления первой микросхемы.

Рис. 15.45

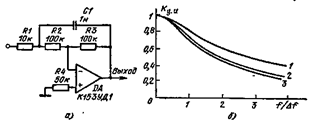

Транзисторный дифференциатор. Дифференциатор (рис. 15.45, а) построен на основе транзисторного каскада с ОБ. Частотные характеристики для низких и высоких частот показаны на рис. 15.45, б. Как видно из рисунков, амплитуда выходного сигнала пропорциональна частоте. На высоких частотах при С1<10 нф наблюдается явление резонанса, которое обусловлено паразитными емкостями транзисторов.

Дата публикования: 2014-11-04; Прочитано: 1284 | Нарушение авторского права страницы | Мы поможем в написании вашей работы!