|

Главная Случайная страница Контакты | Мы поможем в написании вашей работы! | |

Структура системы автоматического управления

|

|

Допустим, логический элемент должен выдать сигнал при условии, что на вход будут одновременно поданы три входных сигнала. Эту функцию выполняет элемент И

Для срабатывания элемента X (электромагнитного реле) необходимо подать сигналы (напряжения) на обмотки трех реле —я3, которые замкнут свои контакты, изображенные в таблице. При этом поступит напряжение на обмотку реле Х. Выходной сигнал появится после замыкания контакта х.

Логические функции, выполняемые элементами, могут быть обозначены алгебраически.

Если отсутствует хотя бы один входной сигнал (допустим, ai = 0), то выходной сигнал также равен 0.

12.7. ПОЛУПРОВОДНИКОВЫЕ ТРАНЗИСТОРНЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

Рассмотрим работу первого элемента. При отсутствии сигналов на входах 1, 3, 5, 7 транзистор VT1 закрыт напряжением смещения +t/CM. При этом напряжение на его коллекторе (выход 9) практически равно напряжению источника. На выходе элемента имеем логическую единицу, равную по значению напряжению источника — 12 В. При подаче на любой из входов 1, 3, 5, 7 отрицательного напряжения от —4 до —12 В транзистор VT1 открывается и напряжение на выходе 9 практически падает до U3к насыщения. На выходе появляется логический нуль. Элемент реализует логическую функцию У=Х1-\-Х2+Хп. Логический элемент серии Т-101 может питать элемент серии Т-107, выполняющий функцию И.

Логический элемент серии Т-101, выполняющий функцию ИЛИ—НЕ (а), и его временные диаграммы (<5)

Логический элемент серии Т-101, выполняющий функцию ИЛИ—НЕ (а), и его временные диаграммы (<5)

|

Более совершенная серия «Логика И» выполнена на интегральных микросхемах, имеет меньшие габариты и лучшие технические характеристики. Вход выполнен на двух транзисторах VT1 и VT2 типа р-п-р. В качестве транзисторов VT3, VT4, VT5 использованы транзисторные структуры типа п-р-п. При открытых транзисторах VT1 и VT2 транзистор VT3 закрыт, так как потенциал его базы равен нулю. Рассмотрим работу схемы при шунтированном стабилитроне VD2. Если закрыт транзистор VT3, то закрыт транзистор VT5. При этом транзистор VT4 открыт и выходное напряжение UBblx близко к напряжению источника (+15 В). На выходе элемента выдается логическая единица. Если на оба входа Х\ и X ? подать положительное напряжение, закрывающее оба транзистора VT1 и VT2, то под действием тока 6 открывается VT3. При этом VT5 также открывается и напряжение на выходе падает до логического нуля. Транзистор VT4 закрывается падением напряжения, образующимся на прямом сопротивлении диода VD3. Транзисторы VT3 и VT5 работают как один составной транзистор. Ток коллектора VT3 является открывающим током для VT5, и оба транзистора либо открыты, либо закрыты. Для выравнивания их эмиттерных токов параллельно эмиттерному переходу транзистора VT5 включается резистор R5. Этот же резистор обеспечивает закрытие VT5. Такое включение VT3 и VT5 позволяет повысить коэффициент усиления. Следует отметить, что к выходу элемента может быть подключено много других логических элементов, которые создают эквивалентную емкость на выходе (до 680 пФ). Заряд этой емкости происходит через небольшой резистор R4 и транзистор VT4, а разряд — через VD3 и VT5. Благодаря малой постоянной времени заряда и разряда время срабатывания элемента мало: 250—500 мс.

Для повышения помехоустойчивости элемента включен стабилитрон VD2. До тех пор, пока напряжение на нем менее 6 В, транзисторы VT3 и VT5 не открываются.

Для увеличения числа управляющих сигналов параллельно транзисторам VT1 и VT2 могут включаться дополнительные транзисторы типа р-п-р.

Основные параметры элемента К-511

Напряжение питания, В - 15±10%

Логическая единица, В, не менее 12

Логический нуль, В, не менее 1,5

Пороговое значение логического нуля, В – 6

Статическая помехоустойчивость по постоянному току, В – 4,5

Частота переключений, кГц, не менее 10

12.8. ПОЛУПРОВОДНИКОВЫЕ ФУНКЦИОНАЛЬНЫЕ ЭЛЕМЕНТЫ

К логическим элементам относятся триггеры, являющиеся элементами памяти. В триггере на основе электромагнитного реле при нажатии кнопки х подается напряжение на его обмотку У. Реле кроме главного контакта имеет вспомогательный контакт у, который при замыкании кнопки х1 шунтирует ее после срабатывания. Поэтому после размыкания кнопки х1 токи в нагрузке и обмотке реле остаются. Нагрузка обесточивается при нажатии кнопки х2. Таким образом, в схеме реализуется функция памяти.

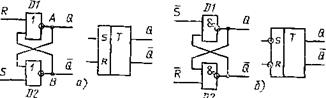

Логическая функция триггера может быть записана в виде У= (xi~j-y)x2. Преимущественное распространение получили полупроводниковые триггеры типов RS, //(, Т и D. В ^S-триггере используются логические элементы ИЛИ—НЕ и И—НЕ (рис. 12.39) и имеются вход S (английский термин set — установка) и вход R (английский термин reset — сброс). Выход Q триггера называют прямым, выход Q — инверсным. По обоим выходам элементы триггера D1 и D2 охвачены перекрестными обратными связями.

|

Рассмотрим работу схемы. Пусть на входах R и S сигналы отсутствуют. При этом на выходе Q могут устанавливаться логические 0 или 1. Допустим, Q = 0. Если подать сигнал на вход S, то на выходе В устанавливается 0. На входе R при этом сигнала нет, и на выходе элемента D1 устанавливается 1, так как на второй вход элемента D1 пулевой сигнал подается с выхода D2. Если со входа S сигнал снять, то на выходе элемента D2 сигнал отсутствует (0) из-за наличия сигнала обратной связи от элемента DL Если подать сигнал на вход вторично, то состояние триггера не изменится. На выходе А устанавливается 1, на выходе В—0. Если подать сигнал на вход /?, то на выходе А устанавливается нулевой сигнал, при этом на вход элемента D2 подается два логических нуля и на выходе элемента D2 устанавливается 1. При снятии сигнала со входа R состояние элемента А не изменится (Q = 0), так как на него действует сигнал обратной связи с элемены’ D2. Одновременная подача сигналов па входы S и R приводит к неопределенному состоянию триггера. Такая возможность должна быть в схеме исключена.

Если до подачи сигнала на вход S на выходе элемента Dl сигнал Q = l, то это автоматически определяет сигнал на выходе Bt равный нулю (Q = 0). При подаче сигнала на вход S состояние триггера не меняется.

Подадим сигнал 0 на вход S и сигнал 1 на вход R. Так как на элементе D1 один из входов имеет 0, то на его выходе устанавливается 1 вне зависимости от сигнала на втором входе. По цепи обратной связи эта 1 будет подана на второй вход элемента D2. Поскольку на входе D2 имеем две логические 1, то на его выходе устанавливается 0. При сигналах R — 0, S — 1 и наличии Q = 1 и Q=0 на

Рис 12. 39 Асинхронные S-триггеры. а —с прямыми входами, б — с инверсными входами

Рис 12. 39 Асинхронные S-триггеры. а —с прямыми входами, б — с инверсными входами

|

выходе элемента D2 устанавливается 1, так как один из его входов имеет 0 (/? = 0). По цепи обратной связи эта 1 передается на элемент D7, и на его выходе появляется 0, так как на вход подано две логические единицы. Происходит сброс триггера. При R=S = l триггер сохраняет предыдущее состояние.

Триггер на элементах И—НЕ является инверсным относительно триггера на элементах ИЛИ—НЕ (см. рис. 12.39,а), так как он переходит в состояние Q=1 и Q = 0 при подаче сигнала S = 0 и R= 1. Значения R = 0, S = 0 должны быть исключены, так как такое их сочетание приводит к неопределенному состоянию триггера.

Описанные триггеры называются асинхронными, так так они могут изменять свое состояние немедленно после появления входных сигналов. При этом возможно нарушение логических связей, обусловленное тем, что выходные сигналы обратной связи различных элементов из-за переходных процессов образуются не одновременно Из-за этого появляются ложные сигналы, нарушающие нормальную работу схем управления.

Для устранения этого недостатка вводится синхронизирующий вход С, который запускает триггер. Па входах RS- триггера, содержащего элементы И— НЕ, стоят два элемента И—НЕ. На вход R сигнал подается только тогда, когда одновременно подаются сигналы Xs и Хс. Сигнал на выходе Q = 1 устанавливается только тогда, когда в момент времени £2 появляются Xs— 1 и Хс— 1. Обратное состояние триггера появляется в момент времени £3 при наличии сигналов XR=l и Хс = = 1. Обычно синхронизированные триггеры имеют дополнительные входы, показанные штриховой линией, для установки в исходное положение.

Допустим, что состояние выходов Q = 1_ и Q = 0. Подадим сигналы / = 1 и К = 0. На входах S и R имеем 1. Триггер не меняет своего состояния. Если <2 = 0 и Q — 1, то на входе S получается 0, а на входе R устанавливается 1. Происходит переброс триггера в состояние <2=1 и <2 = 0. Если затем подать сигналы J*— 0 и К— = 1, то триггер переходит в состояние Q = 0 и Q = l. На входы / и К можно одновременно подать логические 1. Если <2=1 и Q = 0, то на входе S устанавливается 1 и на входе R —0. Происходит переброс триггера в состояние <2 = 0 и Q = 1. Если снова подать 1 на оба входа, то триггер переходит в состояние <2=1 и Q=0. Таким образом/К-

триггер может работать при одновременной подаче сигнала 1 на оба входа. Триггеры RS при одновременной подаче единичного сигнала на оба входа имеют неопределенное состояние.

При каждой подаче одного сигнала на вход происходит инвертирование сигналов на выходах.

Триггер имеет вход D и синхронизирующий вход 7\ При отсутствии сигнала на входе D Q=0 и Q=l. Если сигнал па вход D приходит в момент времени /ь состояние триггера не меняется. В момент t2 прихода синхроимпульса на вход Т происходит переброс триггера в положение Q= 1, Q — 0. После прохождения синхроимпульса и снятия сигнала D состояние триггера не меняется, пока не придет следующий синхроимпульс (до момента времени ti).

Рис. 12.42. Схема и временная диаграмма D-триггера

Таким образом, D-триггер сохраняет состояние логической 1 после снятия входного сигнала до прихода очередного синхроимпульса.

Таким образом, D-триггер сохраняет состояние логической 1 после снятия входного сигнала до прихода очередного синхроимпульса.

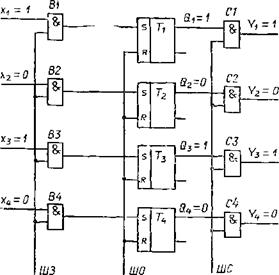

Для записи двоичных чисел служат регистры. Регистр состоит из двоичных ячеек, число которых соответствует числу разрядов — длине кода.

Регистр имеет три общие шины: шины установки нуля ZZ/0, шину записи ШЗУ шину считывания ШС. При подаче напряжения на шину ШО все триггеры устанавливаются на нуль (происходит очистка памяти). При подаче напряжения на шину ШЗ срабатывают элементы И (В1 — В4) и сигнал подается на входы /^S-триггеров. Для считывания информации из регистра подается сигнал на шину ШС. На выходе регистров включены четыре элемента И (С!—С4), выдающие сигнал Y после подачи напряжения на шипу ШС. При считывании состояние регистров не меняется. За писанная информация может использоваться многократно. Цифровая информация может записываться в регистрах последовательного действия. Сначала записывается старший разряд, а потом младшие.

Асинхронный параллельный регистр

Дешифратор — это логическая схема, которая каждую комбинацию сигналов на его входе (код) в результате обработки информации выдает в виде определенного сигнала на его выходе. Такая операция широко используется при автоматическом управлении. Дешифраторы также используются при переходе из одной системы счисления в другую. Дешифраторы реализуются на триггерных узлах и имеются в серии «Логика И».

Для электрической развязки выходов логических элементов от присоединяемого оборудования и повышения выходной мощности широко применяются выходные элементы в виде герконовых реле (И-201—И-204, И-206, И-401 — И-403). Однако герконы обладают таким недостатком, как возможность вибрации контактов. Если вибрации контактов недопустимы, то применяется выходной элемент И-406 на оптоэлектронных приборах. При подаче сигнала на контакты 2, 5 подается напряжение на фотодиоды, излучение которых открывает фототиристоры. В результате сопротивление между точками 8У 12 резко падает и через нагрузку потечет ток. Наличие в схеме двух тиристоров обеспечивает прохождение через нагрузку переменного тока. Цепочка RC служит для ограничения перенапряжений на тиристорах.

12.9. БЕСКОНТАКТНЫЕ КОММУТИРУЮЩИЕ И РЕГУЛИРУЮЩИЕ

ПОЛУПРОВОДНИКОВЫЕ УСТРОЙСТВА ПЕРЕМЕННОГО ТОКА

(БКРПУ)

На основе тиристоров возможно осуществление следующих операций:

1. включение и отключение электрической цепи с активной и смешанной (индуктивной и емкостной) нагрузкой;

2. изменение тока нагрузки за счет регулирования момента подачи сигнала управления.

Напряжение на нагрузке при фазовом (а), фазовом с принудительной комму гацией (б) и широтно-импульсном (в) управлении

Напряжение на нагрузке при фазовом (а), фазовом с принудительной комму гацией (б) и широтно-импульсном (в) управлении

|

Наиболее широкое применение в бесконтактных электрических аппаратах получили фазовое и широтно-импульсное управление.

В первом случае среднее и действующее значения тока Меняются за счет изменения момента подачи на тиристор открывающего сигнала за счет угла а. Угол а называется углом управления.

Встречно-параллельное включение тиристоров (а) и форма тока при активной нагрузке (б)

Дата публикования: 2015-11-01; Прочитано: 688 | Нарушение авторского права страницы | Мы поможем в написании вашей работы!