|

Главная Случайная страница Контакты | Мы поможем в написании вашей работы! | |

Организация памяти микропроцессорных систем

|

|

Рисунок 3.31 – Типичные сигналы ЗУ

Рисунок 3.32 – Классификация полупроводниковых ЗУ

Рисунок 3.32 – Классификация полупроводниковых ЗУ

Рисунок 3.33 – Структура ОЗУ типа 2D

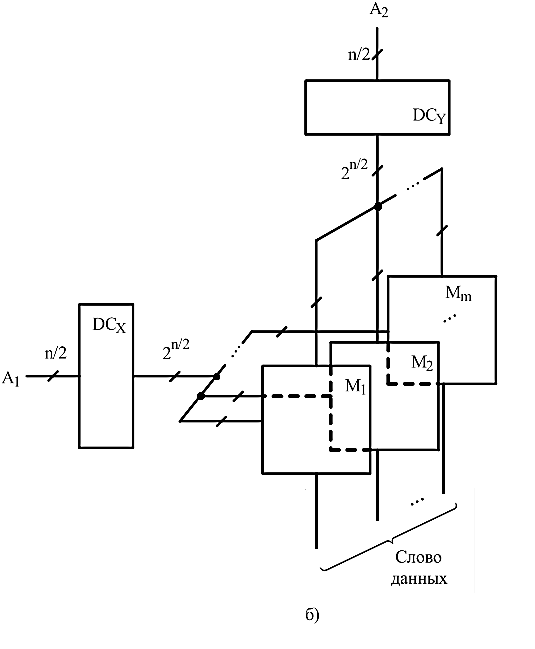

Рисунок 3.34 – Структура постоянного ЗУ типа 3D с одноразрядной (а) и многоразрядной организациями (б)

Окончание рисунка 3.34

Рисунок 3.35 – Структура ЗУ типа 2DM для ROM

Рисунок 3.36 – Структура ЗУ типа 2DM для RAM

Рисунок 3.37 – Структура Кэш-памяти

Рисунок 3.38 – Структура полностью ассоциативной Кэш-памяти

Рисунок 3.39 – Принципиальная электрическая схема ЗЭ на КМОП-транзисторах

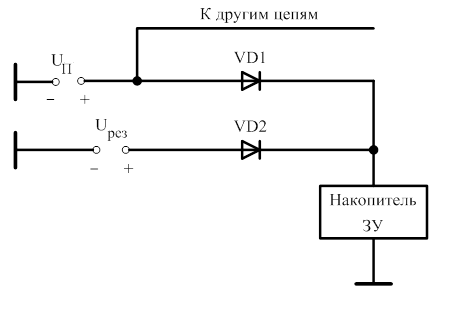

Рисунок 3.40 – Схема подключения резервного источника питания к накопителю ЗУ

Рисунок 3.41 – Принципиальная схема ЗЭ динамического ОЗУ

Рисунок 3.42 – Схема включения усилителя-регенератора в разрыв линии записи-считывания динамического ЗУ (а) и вариант схемной реализации усилителя-регенератора (б)

Рисунок 3.43 – Матрица диодных запоминающих элементов масочного ПЗУ

Рисунок 3.44 – Запоминающие элементы с плавкими перемычками (а) и диодными парами (б)

Рисунок 3.45 – Структуры транзисторов типов МНОП (а) и ЛИЗМОП с двойным затвором (б)

Рисунок 3.46 – Схема подключения ЛИЗМОП-транзисторов с двойным затвором к линиям выборки и считывания в РПЗУ

Рисунок 3.47 – Структура матрицы накопителя Флэш-памяти на основе ячеек ИЛИ-НЕ

3.7 ИНТЕРФЕЙСНЫЕ БИС/ СБИС

Рисунок 3.48 – Шинный формирователь КР580ВА86. Схема логическая (а) и временные диаграммы работы (б)

t1 – задержка распространения сигналов от входов к выходам;

t2 – задержка перехода выходов в Z-состояние;

t3 – задержка перехода выходов в активное состояние;

t4 и t5 – время выдержки и предустановки сигнала T относительно сигнала  .

.

б)

Окончание рисунка 3.48

Рисунок 3.49 – Буферный регистр КР580ИР82. Схема логическая (а) и временные диаграммы работы (б)

t1 – задержка распространения сигналов от входов к выходам;

t2 – задержка перехода выходов в Z-состояние;

t3 – задержка перехода в активное состояние;

t4 – интервал от изменения строба до изменения выхода схемы;

t5 и t6 – времена предустановки и выдержки входного сигнала относительно спада строба ( ).

).

б)

Окончание рисунка 3.49

Таблица 3.11 – Адресация внутренних регистров ППА и направление передач

Дата публикования: 2015-09-17; Прочитано: 788 | Нарушение авторского права страницы | Мы поможем в написании вашей работы!