|

Главная Случайная страница Контакты | Мы поможем в написании вашей работы! | |

Архитектура микропроцессора Intel 8086

|

|

Цель и содержание работы

Целью работы является изучение архитектуры микропроцессора Intel 8086 с помощью персонального компьютера семейства IBM PC и его программного обеспечения (Turbo Assembler, Turbo Debugger).

Продолжительность работы

Работа рассчитана на три четырёхчасовых занятия, включая один час на проведение коллоквиума для оценки знаний студентов по теоретической части.

Теоретическая часть

Для выполнения данной лабораторной работы требуются знания в области архитектуры микропроцессора Intel 8086: структуры микропроцессора, методов адресации, форматов и системы команд, особенностей программирования и отладки программ на ассемблере.

Архитектура микропроцессора Intel 8086

16-битный микропроцессор 8086 (отечественный аналог КР1810ВМ86) содержит на кристалле около 29000 транзисторов и производится по высококачественной n- МОП технологии. Число линий адреса равно 20, что позволяет адресовать память 1МБ. Кроме того, в микропроцессоре 8086 встроены некоторые средства, упрощающие реализацию мультипроцессорных систем (максимальный режим работы), что позволяет применять его с другими процессорами, например, с сопроцессором числовых данных 8087.

3.1.1. Структура микропроцессора

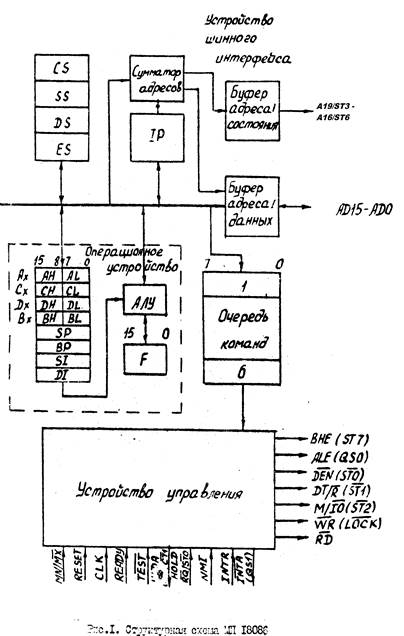

Назначение выводов микропроцессора (МП) зависит от режима его работы (см. рис. 1), причем обозначения в скобках на рис.1 соответствуют минимальному режиму. В табл.1 – приведено назначение выводов МП, являющихся общими для обоих режимов, в табл.2 – назначение выводов, используемых только в минимальном режиме, в табл.3 – используемых только в максимальном режиме. Буквой (Z) отмечены трех- стабильные выходы, которые переводятся в третье (высокоомное) состояние при переходе микропроцессора в режим ПДП- прямого доступа к памяти.

Структурная схема МП 8086 содержит две относительно независимые части: операционное устройство, реализующие заданные командой функции, и устройство шинного интерфейса, осуществляющее выборку команд и обращение к памяти и внешним устройствам для считывания операнда и записи результатов, а также блок управления. Оба устройства могут работать параллельно, что обеспечивает во времени совмещение процессов выборки и исполнения команд. Это повышает быстродействие микропроцессора, т.к. операционное устройство, как правило, выполняет команды, коды которых уже находятся в микропроцессоре, и поэтому такты выборки команд не включаются в цикл.

Операционное устройство микропроцессора содержит группу регистров общего назначения (РОН), арифметико-логическое устройство (АЛУ), регистр флагов F и ряд вспомогательных устройств. Восемь 16-битовых РОН участвуют во многих командах. В этих случаях регистры общего назначения кодируются трех битовым кодом, который размещается в соответствующем поле (или полях) формата команды.

В соответствии с основным назначением рассматриваемых регистров выделяют регистры AX, BX, DX, CX, используемые, прежде всего для хранения данных, и регистры SP, BP, SI, DI, которые хранят главным образом, адресную информацию. Особенностью регистров AX, BX, DX, CX является то, что они допускают раздельное использование их младших байтов AL, BL, CL, DL и старших байтов AH, BH, CH, DH. Тем самым обеспечивается возможность обработки как слов, так и байтов и создаются необходимые условия для программной совместимости 8086 и 8080. Все остальные регистры являются неделимыми и оперируют 16 – битовыми словами, даже в случае использования старшего и младшего байтов.

Кроме основных функций, соответствующих назначению регистров, общие регистры выполняют специальные функции, указанные в табл.4.

Арифметико-логическое устройство (АЛУ) содержит 16-битовый комбинационный сумматор, с помощью которого выполняются арифметические операции, наборы комбинационных схем для выполнения логических операций, схемы для операций сдвигов и десятичной коррекции, а также регистры для временного хранения операндов и результатов.

Управляющее устройство дешифрирует команды, а также воспринимает и вырабатывает управляющие сигналы. В его состав входит блок программного управления, в котором реализовано программирование МП на микрокомандном уровне.

Устройство шинного интерфейса содержит блок сегментных регистров, указатель команд – регистр IP, сумматор адресов, очередь команд и буферы, обеспечивающие связь с шиной.

Очередь команд представляет собой наборы байтовых регистров и выполняет роль регистра команд, в котором хранятся коды, выбранные из программной памяти. Длина очереди составляет 6 байт, что соответствует максимально длинному формату команд. Шинный интерфейс инициирует выборку следующего командного слова автоматически, как только в очереди освободятся два байта.

Буфер шины адреса/данных (БАД) содержит 16 двунаправленных управляемых усилителей с тремя выходными состояниями и обеспечивает номинальную нагрузочную способность линий AD0-AD15.

|

Буфер шины адреса/состояния (БАС) содержит четыре однонаправленных усилителя с тремя выходными состояниями и обеспечивает номинальную нагрузочную способность линий A19/S6-A16/S3.

Таблица 1.

Дата публикования: 2015-11-01; Прочитано: 2118 | Нарушение авторского права страницы | Мы поможем в написании вашей работы!