|

Главная Случайная страница Контакты | Мы поможем в написании вашей работы! | |

Триггеры

|

|

Триггер (бистабильный мультивибратор) — это цифровой автомат, имеющий несколько входов и 2 выхода. Триггер — один из базовых (основных) элементов цифровой техники. Некоторые исследователи включают триггер в 100 великих изобретений.

Триггер не является логическим элементом первого уровня, а сам состоит из логических элементов первого уровня - инверторов или логических вентилей. По отношению к логическим элементам первого уровня триггер является логическим устройством второго уровня. Триггер — элементарная ячейка оперативной памяти.

Триггер - простейшее устройство выполняющее логическую функцию с обратной связью, т.е. простейшее устройство кибернетики.

N-ичный триггер — устройство (элементарная переключаемая ячейка памяти, переключатель с N устойчивыми положениями), которое имеет N устойчивых состояний и возможность переключения из любого состояния в любое другое состояние.

В графе триггера каждая вершина графа соединена со всеми другими вершинами, при этом переходы от вершины к вершине возможны в обе стороны (двухсторонние). В графе счётчика и кольцевого регистра сдвига каждая вершина соединена только с двумя соседними вершинами и переходы между вершинами — односторонние. Граф двоичного триггера — две точки соединённые отрезоком прямой линии, троичного триггера — треугольник, четверичного триггера — квадрат с диагоналями, пятеричного триггера — пятиугольник с пентаграммой и т. д. При N=1 граф триггера вырождается в одну точку, в математике ему соответствует унарная единица или унарный ноль, а в электронике — монтажная «1» или монтажный «0», то есть простейшее ПЗУ.

Счётчик имеет сколько угодно устойчивых состояний, но только счётчик на 2 и реверсивный счётчик на 3 являются триггерами, в остальных счётчиках нет переключения из любого состояния в любое из других состояний. Граф троичного реверсивного счётчика — треугольник, четверичного реверсивного счётчика — квадрат без диагоналей. Граф нереверсивного счётчика на 3 — тоже треугольник, но переходы от вершины к вершине только в одну сторону (односторонние), поэтому он триггером не является.

Регистр сдвига имеет сколь угодно устойчивых состояний, но только регистр сдвига на 2 и реверсивный регистр сдвига на 3 являются триггерами, в остальных регистрах сдвига нет переключения из любого состояния в любое из других состояний. Граф троичного реверсивного регистра сдвига — треугольник, четверичного реверсивного регистра сдвига — квадрат без диагоналей. Граф нереверсивного регистра сдвига на 3 — треугольник, но переходы от вершины к вершине только в одну сторону (односторонние), поэтому он триггером не является.

Триггерные схемы классифицируют по следующим признакам:

- числу целочисленных устойчивых состояний (основанию системы счисления) (обычно устойчивых состояний два, реже — больше);

- числу уровней — два уровня (высокий, низкий) в двухуровневых элементах, три уровня (положительный, ноль, отрицательный) в трёхуровневых элементах, N-уровней в N-уровневых элементах;.

- принципу построения;

- функциональным возможностям;

- способу приёма логических сигналов.

По способу работы с сигналами различают асинхронные, синхронные и смешанные триггерные схемы, статические и динамические.

Асинхронный триггер изменяет своё состояние непосредственно в момент появления соответствующего информационного сигнала.

Синхронные триггеры реагируют на информационные сигналы только при наличии соответствующего сигнала на так называемом входе синхронизации С (от англ. clock). Этот вход также обозначают терминами «строб», «такт». Синхронные триггеры в свою очередь подразделяют на триггеры со статическим и динамическим управлением по входу синхронизации С.

Статические триггеры воспринимают информационные сигналы при подаче на вход С логической единицы (прямой вход) или логического нуля (инверсный вход).

Динамические триггеры воспринимают информационные сигналы при изменении (перепаде) сигнала на входе С от 0 к 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход).

Статические триггеры в свою очередь подразделяют на одноступенчатые (однотактные) и двух-ступенчатые (двухтактные).

В одноступенчатом триггере имеется одна ступень запоминания информации, а в двухступенчатом — две такие ступени. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе (обычно двухступенчатые триггеры применяются в схемах, где логические функции входов триггера зависят от его выходов, во избежание временных гонок). Двухступенчатый триггер обозначают ТТ.

По структурному построению — однотактные (триггеры защёлки), двухтактные и триггеры с динамическим управлением. По способу реакции на помехи — прозрачные и непрозрачные. Непрозрачные, в свою очередь, делятся на проницаемые и непроницаемые. По функциональному назначению — RS, D, JK, T, RR, SS, EE, DV.

При изготовлении триггеров применяются преимущественно полупроводниковые приборы (обычно полевые транзисторы), в прошлом — электромагнитные реле, электронные лампы. В настоящее время логические схемы, в том числе с использованием триггеров, создают в интегрированных средах разработки под различные программируемые логические интегральные схемы (ПЛИС).

Используются в основном в вычислительной технике для организации компонентов вычислительных систем: регистров, счётчиков, процессоров, ОЗУ.

По функциональным возможностям триггеры разделяют на следующие классы:

- с раздельной установкой состояния 0 и 1 (RS-триггеры). Если триггер является синхронным — добавляется вход синхронизации C.;

- универсальные (JK-триггеры);

- с приёмом информации по одному входу D (D-триггеры, или триггеры задержки);

- со счётным входом Т (Т-триггеры).

Каждый тип триггера имеет собственную таблицу работы (таблицу истинности). Выходное состояние триггера обычно обозначают буквой Q. Индекс возле буквы означает состояние до подачи сигнала (t) или после подачи сигнала (t+1).

Если триггер синхронный, то существует также дополнительный вход синхронизации. Для того, чтобы такой триггер учёл информацию на синхронных входах, на входе синхронизации необходимо сформировать активный фронт (обычно положительный фронт).

Входы триггеров обычно обозначают следующим образом:

- S (от англ. Set, установить) — вход в RS-триггере;

- R (от англ. Reset, сброс) — вход в RS-триггере;

- J (от англ. Jump, прыжок) — вход в JK-триггере;

- К (от англ. Kill, убить) — вход в JK-триггере;

- Т (от англ. Toggles, переключить) — счётный вход в Т-триггере;

- С (от англ. Clock, время) вход синхронизирующего сигнала. При тактировании по фронту он часто обозначается стрелкой: стрелка внутрь — тактирование по переднему фронту, наружу — по - заднему.

- D (от англ. Delay, задержка) — вход в D-триггере;

- E или EN (от англ. Enable, разрешить) — дополнительный асинхронный управляющий вход для разрешения приёма информации (иногда используют букву V).

Входы J,К,Т,D всегда синхронные, то есть тактируются по синхронизирующему сигналу на входе C. Разумеется, в каждом конкретном триггере имеются лишь некоторые из перечисленных входных линий. Входы S и R зачастую присутствуют не только в RS триггерах, но и в других типах триггеров, где предназначены, в основном, для асинхронного сброса устройства в 0 или установки в 1.

В некоторых устройствах встречаются инверсные входы. Как и инверсный выход, на обозначении триггера инверсный вход содержит кружок, а соответствующая ему буква надчёркнута.

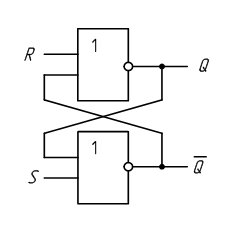

RS-триггер, или SR-триггер — триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё выходное состояние при подаче на один из его входов единицы. При подаче единицы на вход S выходное состояние становится равным логической единице. А при подаче единицы на вход R выходное состояние становится равным логическому нулю. Если RS-триггер синхронный, то состояние его входов учитывается только в момент тактирования, например по переднему фронту импульса. Состояние, при котором на оба входа R и S одновременно поданы логические единицы, является запрещённым. Так, например, схема RS-триггера, изображённая на рис. 9.1, при подаче на оба инверсных входа логического нуля перейдёт в состояние, когда на обоих выходах будут единицы, что не соответствует логике выхода триггера, поскольку инверсный выход  будет равен неинверсному

будет равен неинверсному  , то есть

, то есть  .

.

рис. 9.1

RS-триггер используется для создания сигнала с положительным и отрицательным фронтами, отдельно управляемыми посредством стробов, разнесённых во времени. RS-триггеры иногда называют RS-фиксаторами

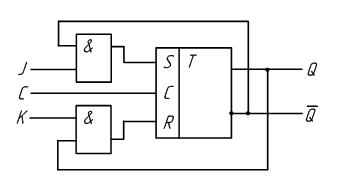

JK-триггер работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J аналогичен входу S у RS-триггера. Вход K аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и K учитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации.

рис. 9.2

На базе JK-триггера возможно построить D-триггер или Т-триггер. JK-триггер переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К.

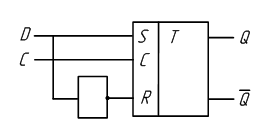

D-триггер — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. Сохранение информации в D-триггерах происходит в момент прихода активного фронта на вход С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы.

рис. 9.3

D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине.

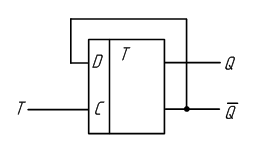

Т-триггер по каждому такту изменяет своё логическое состояние на противоположное при единице на входе Т, и не изменяет выходное состояние при нуле на входе T. Т-триггер часто называют счётным триггером. Т-триггер может строиться как на JK, так и на D-триггерах. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединяя входы J и К. Наличие в D-триггере динамического С входа позволяет получить на его основе T-триггер. При этом вход D соединяется с инверсным выходом, а на вход С подаются счётные импульсы. В результате триггер при каждом счётном импульсе запоминает значение  , то есть будет переключаться в противоположное состояние.

, то есть будет переключаться в противоположное состояние.

рис. 9.4

Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена.

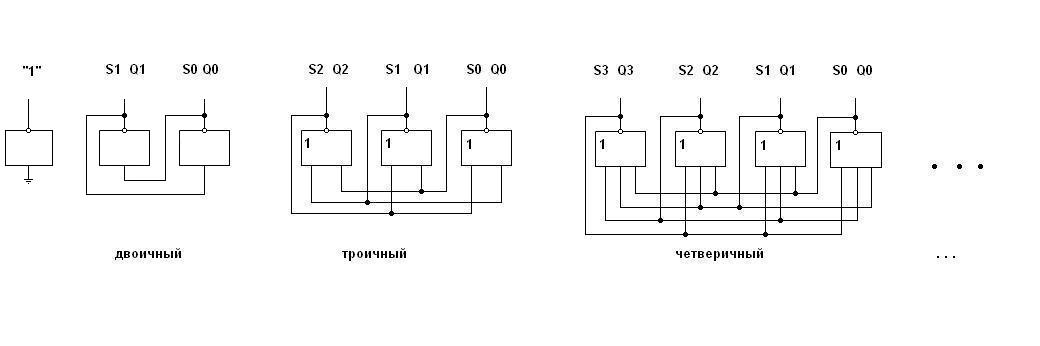

Триггер с любым числом устойчивых состояний N строится из N элементов (N-1)ИЛИ-НЕ или (N-1)И-НЕ путём соединения выхода каждого элемента (Q0, Q1, …, Q(N-1)) с соответствующими входами всех других элементов. То есть наименьшее число логических элементов для построения N-ичного триггера равно N.

Триггеры на элементах (N-1)ИЛИ-НЕ работают в прямом одноединичном коде (на выходе Q одного из элементов — «1», на выходах Q других элементов — «0»). Триггеры на элементах (N-1)И-НЕ работают в инверсном однонулевом коде (на выходе Q одного из элементов — «0», на выходах Q других элементов — «1»). При добавлении N транзисторов доступа эти триггеры могут работать как ячейки статической сверхоперативной памяти (SRAM). При добавлении схем управления переключением эти триггеры могут работать как N-ичные аналоги двоичного RS-триггера.

По теореме Джона фон Неймана[26] (позиционные системы счисления) наибольшей плотностью записи и наименьшими аппаратными затратами обладают троичные триггеры, второе место занимают двоичные и четверичные триггеры.

рис. 9.5

Дата публикования: 2015-10-09; Прочитано: 698 | Нарушение авторского права страницы | Мы поможем в написании вашей работы!