|

Главная Случайная страница Контакты | Мы поможем в написании вашей работы! | |

Отличие от архитектуры фон Неймана

|

|

В чистой архитектуре фон Неймана процессор одномоментно может либо читать инструкцию, либо читать/записывать единицу данных из/в памяти. То и другое не может происходить одновременно, поскольку инструкции и данные используют одну и ту же системную шину.

А в компьютере с использованием гарвардской архитектуры процессор может читать инструкции и выполнять доступ к памяти данных в то же самое время, даже без кэш-памяти. Таким образом, компьютер с гарвардской архитектурой может быть быстрее (при определенной сложности схемы), поскольку доставка инструкций и доступ к данным не претендуют на один и тот же канал памяти.

Также машина гарвардской архитектуры имеет различные адресные пространства для команд и данных. Так, нулевой адрес инструкций — это не то же самое, что и нулевой адрес данных. Нулевой адрес инструкций может определяться двадцатичетырехбитным значением, в то время как нулевой адрес данных может выглядеть как восьмибитный байт, который не являются частью этого двадцатичетырехбитного значения

Архитектура фон Неймана — широко известный принцип совместного хранения команд и данных в памяти компьютера. В общем случае, когда говорят об архитектуре фон Неймана, подразумевают физическое отделение процессорного модуля от устройств хранения программ и данных.

Принцип однородности памяти Прогр и данные хран в одной и той же памяти.ЭВМ не различает, что хранится в данной яч памяти — число,текст,команда. Над команд м выполнять те же действия, как и над данными.

Принцип адресуемости памяти Основная память структурно состоит из пронумерованных ячеек; процессору в произвольный момент времени доступна любая ячейка. Отсюда следует возможность давать имена областям памяти, так, чтобы к хранящимся в них значениям можно было бы впоследствии обращаться или менять их в процессе выполнения программы с использованием присвоенных имен.

Принцип последовательного программного управления Предполагает, что программа состоит из набора команд, которые выполняются процессором автоматически друг за другом в определенной последовательности.

Принцип жесткости архитектуры. Неизменяемость в проц-се работы топологии, арх-туры, списка команд.

Так же в некоторых источниках указывается принцип двоичного кодирования, но существовали машины, работающие с троичным и с десятичным кодом.

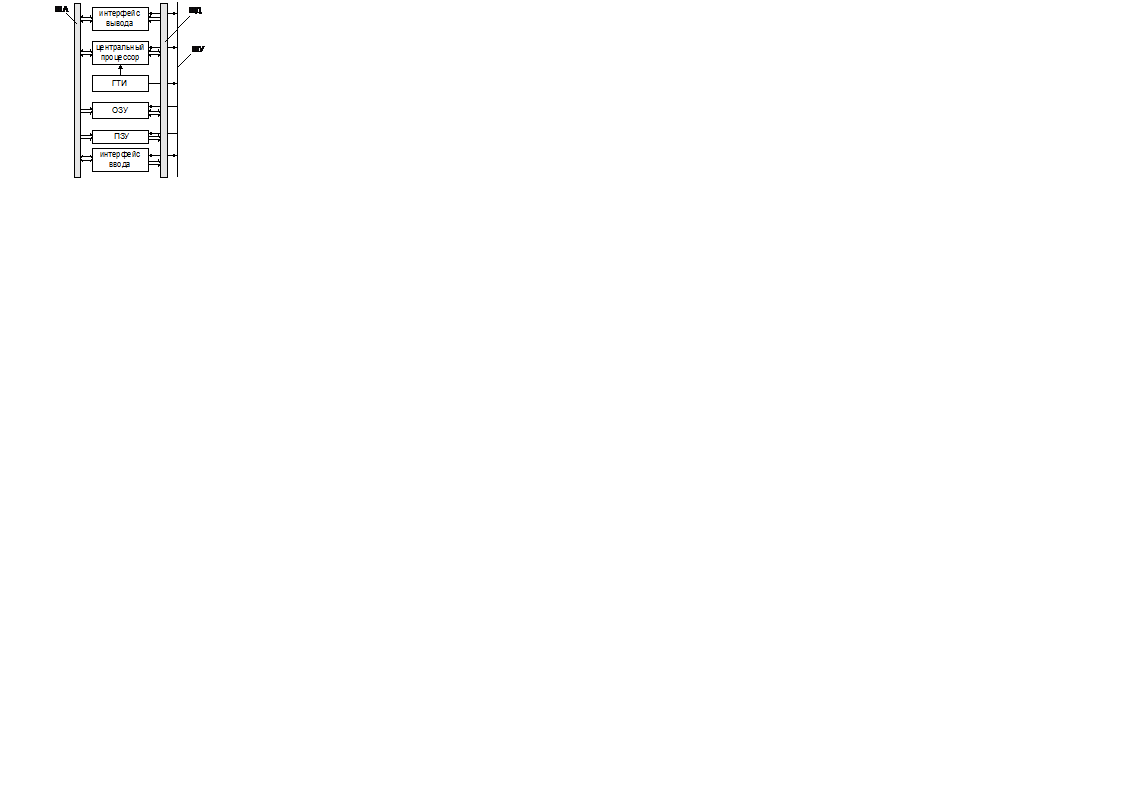

Схема структуры микро ЭВМ:

Схема структуры микро ЭВМ:

ГТИ – генератор тактовых импульсов

Шина – набор параллельных проводников, по которым передается информация

Шина управления (ШУ) – для синхронизации и согласования узлов ЭВМ

Это Фон Неймовская архитектура, т.е. общая для всех устройств шина адреса (ША) и шина данных (ШД), имеется единое адресное пространство. Для обращения к конкретному устройству выделяется свой диапазон адресов, эти диапазоны не пересекаются. Генератор тактовых импульсов формирует две последовательности импульсов смещенные на 90 градусов, они необходимы для синхронизации работы внутренних узлов микропроцессора и совместной работы узлов микро ЭВМ.

В ПЗУ хранятся программы и константы, т.е. данные в ходе выполнения программы не меняются. Данные в ОЗУ меняются в течении работы. Программы на микроЭВМ загружаются в ОЗУ. В ПЗУ хранится BIOS, которая позволяет загружать данные с жесткого диска.

Кроме физического разделения памяти на ПЗУ и ОЗУ память также может быть разделена функционально, на память программ и память данных.

Структура микропроцессора:

·  АЛУ – служит для обработки данных, выполняет арифметические и логические операции (+, -, сдвиг, сравнение, инкрементирование, декрементирование, и, или, не, исключающее или). Содержит два буферных регистра.

АЛУ – служит для обработки данных, выполняет арифметические и логические операции (+, -, сдвиг, сравнение, инкрементирование, декрементирование, и, или, не, исключающее или). Содержит два буферных регистра.

· Аккумулятор (А) – главный регистр микропроцессора, участвует в выполнении большинства операций. При выполнении с двумя операндами один находится в А, в А помещается и результат.

· Регистр состояния (регистр словосостояния программы - PSW) или регистр флагов – его наличие отличает ЭВМ от калькулятора. Этот регистр состоит из набора триггеров (флагов), которые устанавливаются и сбрасываются в зависимости от результатов последней операции и (или) от содержимого А.

Состояние флагов может использоваться для организации ветвлений (условных переходов) в программе.

1. Флаг переноса (заема). Указывает, что последняя арифметическая операция сопровождалась переносом или заемом, в этом случае С=1, если ни переноса ни заема не было С=0.

2. Флаг нуля. Z=1 если содержимое А=0.

3. Флаг знака. N=1 если содержимое А<0.

4. Флаг четности (либо дополнения до четности). Если количество единиц в А не четно, то Р=1 (чаще используется дополнение по четности)

5. Флаг переполнения OV. OV=1 если произошло знаковое переполнение. Знаковое переполнение возникает, если при сложении двух положительных чисел получился отрицательный результат, т.е. произошел перенос из 6го в 7й разряд, либо при сложении двух отрицательных чисел, результат получился положительным, возникает перенос из 7го в 8й разряд.

Счетчик команд. Он содержит адрес ячейки памяти программ подлежащей считыванию. После извлечения байта команды из памяти, содержимое счетчика команд автоматически инкрементируется.

Регистр команд хранит код текущей выполняемой команды.

Дешифратор декодирует выполняемую команду.

Схема управления. В соответствии с результатом декодирования генерируют последовательность управляющих импульсов, обеспечивающую взаимодействие внутренних узлов микропроцессора.

Регистр адреса/памяти содержит адрес яч памяти программ или данных к которой происходит обращение.

Регистры общего назначения B, C, и D используются для временного хранения операндов. В и С составляют регистровую пару, их содержимое, при необходимости могут рассматриваться как единое целое.

Указатель стека содержит адрес вершины стека.

Указатель стека содержит адрес вершины стека.

В зависимости от действий, выполняемых МП, различают следующие типы машинных циклов:

выборка (чтение первого байта команды);

чтение памяти (чтение второго и третьего байтов команды, чтение операнда); запись в память; чтение стека; запись в стек;

ввод данных из внешнего устройства; вывод данных во внешнее устройство; прерывание; останов; прерывание при останове.

Цикл выполнения команды состоит из двух основных фаз: 1 – выборка; 2 – выполнение. В фазе выборки команда считывается из памяти по адресу содержащемуся в счетчике команд (Program Counter). Код операции поступает в регистр команд, декодируется, если команда состоит из нескольких байт, то происходит их считывание. После того команда полностью считана, происходит ее выполнение. Это цикл управления Фон Неймана (цикл выборки выполнения).

Этапы 1, 2, 3 повторяются столько раз, сколько слов имеет команда.

Дата публикования: 2015-10-09; Прочитано: 783 | Нарушение авторского права страницы | Мы поможем в написании вашей работы!