|

Главная Случайная страница Контакты | Мы поможем в написании вашей работы! | |

Основная память

|

|

Основная память (ОП) представляет собой массив запоминающих элементов, организованных в виде ячеек, способных хранить некую единицу информации, обычно один байт. Каждая ячейка имеет уникальный адрес. Ячейки ОП организованы в виде матрицы, а выбор ячейки осуществляется путем подачи разрешающих сигналов на соответствующие строку и столбец этой матрицы. Это обеспечивается дешифратором адреса памяти.

Модуль ввода/вывода

Модуль ввода/вывода (МВВ) обеспечивает подключение к ВМ различных периферийных устройств (ПУ) и обмен информацией с ними.

Порты ввода и порты вывода

Порт – это схема, организующая передачу информации из периферийного устройства ввода в регистр АЛУ и наоборот. Схема обеспечивает электрическое и логическое сопряжение ВМ с подключенным к нему периферийным устройством.

Дешифратор номера порта ввода/вывода

Дешифратор номера порта ввода/вывода (ДВВ) обеспечивает преобразование номера порта в сигнал, разрешающий операцию ввода или вывода на соответствующем порте.

3. Компоненты вычислительных систем: дешифраторы; шифраторы; мультиплексоры; триггеры; асинхронные и синхронные триггеры. Счетчики и делители. Классификация счетчиков. Регистры. Классификация регистров. Регистры памяти. Регистры сдвига.

Счетчик предназначен для подсчета количества единиц информации (счетных импульсов). Поступление единицы информации заключается в воздействии на вход счетчика перепада напряжения 0 – 1 при входе или 1 – 0 при инверсном входе. Так как один импульс содержит тот и другой перепады, то его и отождествляют с единицей информации независимо от типа входа счетчика. Счетчики подразделяются еще по другим классификационным признакам. По назначению различают суммирующие, вычитающие реверсивные; по способу запуска – асинхронные и синхронные; по способу организации переноса – с последовательным, сквозным и параллельным переносами.

Основными параметрами счетчиков являются: разрешающая способность, время установления и емкость.

Разрешающая способность—это минимальный период следования счетных импульсов Tст, при которых сохраняется работоспособность счетчика. Обратная величина характеризует максимальную частоту счета.

Время установления Tуст – это интервал между началом подачи на вход счетного импульса и моментом окончания самого продолжительного переходного процесса в счетчике.

Параметры Tст и Tуст характеризуют быстродействие счетчика.

Емкость счетчика определяется максимальным числом импульсов, которое он может зарегистрировать.

Делители—это те же счетчики, но имеют, как правило, один выход, на котором появляется импульсный сигнал после каждых Kп счетных импульсов. Нередко предусматривается возможность изменять коэффициент деления Kп с помощью специального управляющего кода. В принципе делители можно строить и на основе двоичных счетчиков, подключив к выходам дешифратор какого-либо одного состояния.

В большинстве практических случаев интегральные пересчетные устройства делаются комбинированными – счетчиками-делителями. С этой целью счетчик дополняют дешифратором старшего состояния, выходной сигнал которого может быть использован как сигнал переноса при наращивании разрядности с помощью нескольких микросхем, либо как выходной сигнал делителя.

Регистр — последовательное или параллельное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними.

Регистр представляет собой упорядоченную последовательность триггеров, обычно D, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами.

Фактически любое цифровое устройство можно представить в виде совокупности регистров, соединённых друг с другом при помощи комбинационных цифровых устройств.

Основой построения регистров являются D-триггеры, RS-триггеры.

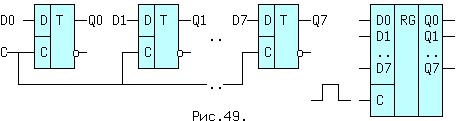

Регистры с параллельной записью называются, также регистрами памяти. В них могут использоваться, как прозрачные "защелки", так и триггеры с динамическим управлением.

На рис.1 приведена схема 8-ми разрядного регистра памяти с общим входом управления записью информацией и ее условное обозначение. Высокий уровень на входе C переписывает информацию с входа на выход (Qi=Di), а низкий уровень - защелкивает данные.

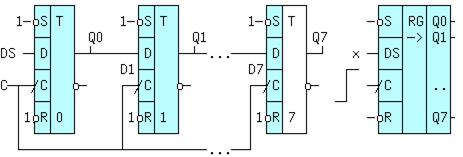

Последовательные регистры или, как их еще называют, регистры сдвига (рис. 2) выполняются на основе триггеров с динамическим синхровходом, (справедливо для регистров с одним тактирующим сигналом). В двухтактных можно использовать и прозрачные регистры - "защелки". Функция записи в n-разрядном регистре сдвига на D-триггерах задается в виде условий: D0=DS=x, Di=Q(i-1), где i=1,2,...,n-1. DS - вход для последовательной записи.

Дата публикования: 2015-09-17; Прочитано: 670 | Нарушение авторского права страницы | Мы поможем в написании вашей работы!