|

Главная Случайная страница Контакты | Мы поможем в написании вашей работы! | |

Режимы работы

|

|

Возможны 3 режима работы портов: 0, 1, 2, причем порт А может работать в любом из 3-х режимов, порт В только в двух режимах (0 и 1), а режим порта С зависит от режимов портов А и В.

Режимы:

| Режим 0 | Однонаправленный ввод/вывод без квитирования, в этом режиме могут работать порты А и В, а также свободные (не занятые передачей служебных сигналов для портов А и В) линии порта С |

| Режим 1 | Однонаправленный ввод/вывод с квитированием |

| Режим 2 | Двунаправленный ввод/вывод с квитированием |

Режим 0.

В режиме 0 базового ввода-вывода могут работать все три порта, причем порт С разделяется на два независимых 4-х разрядных порта. Всего таким образом получается два 8 битных и два 4-х битных порта параллельного ввода и вывода, что обеспечивает 16 возможных вариантов использования адаптера. В портах, запрограммированных для вывода, информация, поступающая с шины данных, фиксируется в буферном регистре порта, а в портах, настроенных на ввод - не фиксируется, т.е. при операции считывания в аккумулятор микропроцессора передается текущее состояние входных линий.

В соответствии с возможностями ввода-вывода в режиме 0 его целесообразно использовать для подключения устройств, у которых обеспечивается синхронность работы с микропроцессором, необходимая для передачи информации без потерь. В случае связи с устройством со сложным протоколом обмена все необходимые сигналы управления с заданными временными соотношениями можно формировать программно через порт С. Однако такой метод использования адаптера связан со значительной нагрузкой на микропроцессор и ограничением скорости обмена.

Режим 1.

В режиме 1 каждая из 2-х 12-разрядных групп (А и В) может быть запрограммирована на однонаправленный ввод или вывод информации с квитированием. При этом входные и выходные данные фиксируются адаптером. По линиям порта С (группы старших и младших байтов) при этом передаются управляющие сигналы. Раздельная установка разрядов порта С позволяет ему играть роль схемы управления процедурами ввода/вывода, причем битам порта придается определенное функциональное назначение.

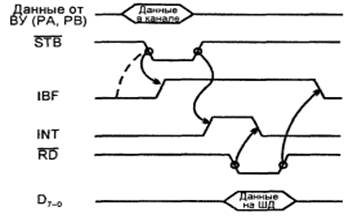

При вводеданных используются следующие управляющие сигналы:

STB – строб загрузки данных в регистр (по заднему фронту);

IBF (Input Buffer Full) – входной буфер полон – выходной сигнал подтверждения загрузки данных;

INT – запрос прерываний.

Временные диаграммы процесса ввода:

Имея данные для ввода в порт, ВУ при условии IBF=0, вырабатывает сигнал готовности информации STB. Передний фронт этого сигнала устанавливает сигнал IBF, запрещающий внешнему устройству ввод следующего слова до освобождения адаптера (того порта, который имеется в виду). К моменту окончания STB данные введены в буфер порта и, если прерывания разрешены (внутренний триггер разрешения прерываний установлен командой программы), то адаптер формирует запрос прерывания для МП. При этом на адаптер поступают сигналы адресации и RD. Передний фронт RD отмечает начало считывания слова микропроцессором и снимает запрос на прерывание. Пока прерывания не разрешены, осуществляется хранение данных в адаптере. Задний фронт RD отмечает завершение считывания слова микропроцессором и снимает сигнал IBF, допуская новую запись слова со стороны ВУ.

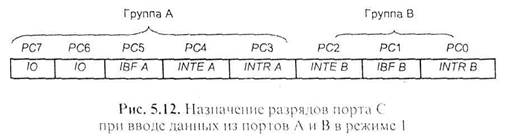

Назначение разрядов порта C при вводе данных из портов А и В в режиме 1 показано на рисунке 5.12.

На рисунке 5.12 INTR (INTeRupt) – выходной сигнал, который сообщает о завершении приема информации; INTE (INTerrupt Enable) – сигнал разрешения прерывания (вход строба приема).

В режиме 1 адаптер может работать как с прерыванием, так и без прерываний. Для работы с прерыванием необходимо, чтобы триггер разрешения прерывания был установлен в состояние 1. При вводе информации роль триггера прерываний для группы А выполняет 4 разряд порта С, а для группы В - второй разряд порта С. Сброс и установка этих триггеров осуществляется программно под управлением микропроцессора.

При разрешении прерывания, после записи в регистр порта очередного информационного слова, триггер запроса прерывания устанавливается в 1 (разряд СЗ для группы А, разряд С0 для группы В) и вырабатывается сигнал «запрос прерывания» (ЗПР). Прием и обработка этого сигнала производится в соответствии с принятой в микропроцессорной системе схемой обработки прерываний. При вводе в режиме 1 остаются неиспользованными 6 и 7 разряды порта С. Они могут быть запрограммированы для ввода или вывода информации независимо от порта А и В.

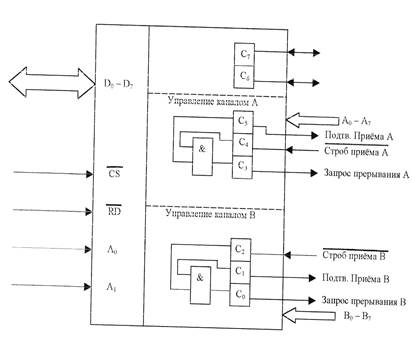

Функциональная схема адаптера при настройке на ввод:

Рис. 1 ВВОД

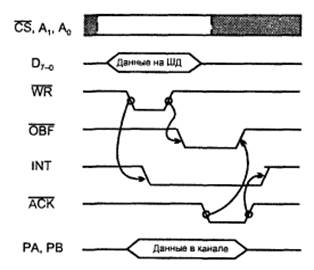

При выводе используются следующие управляющие сигналы:

OBF (Output buffer full) – выходной буфер полон, строб вывода новых данных;

ACK (Acknowledge) – подтверждение приема внешним устройством;

INT – запрос прерываний.

Временные диаграммы процесса вывода:

При выводе выполняется команда OUT port и процессор устанавливает адрес порта и данные на шину данных. При разрешенных прерываниях далее вырабатывается сигнал WR, загружающий данные с шины данных в буфер адаптера и сбрасывающий запрос прерывания INT. После окончания записи в адаптер формируется сигнал OBF, указывающий на готовность данных для ВУ. Приняв данные, ВУ выдает сигнал подтверждения приема ACK, снимающий OBF, а по окончании сигнала ACK восстанавливается запрос прерываний, что вызывает обслуживание следующего цикла вывода.

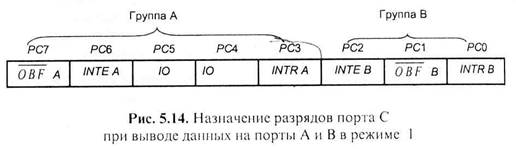

Назначение разрядов порта C при вводе данных из портов А и В в режиме 1 показано на рисунке 5.14.

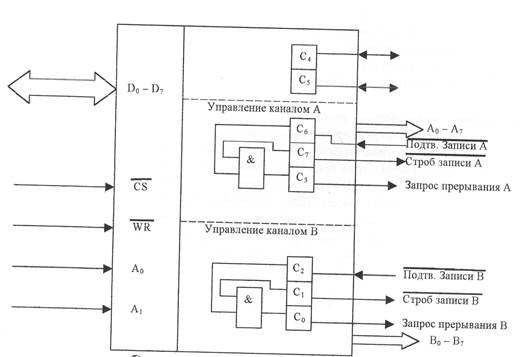

При работе портов А и В на вывод информации функциональная схема адаптера приобретает вид рис. 2. После записи информационного байта вырабатывается сигнал «строб записи», который является признаком готовности к передаче очередного слова во внешнее устройство. После того, как внешнее устройство примет очередной байт информации, оно вырабатывает сигнал «подтверждение записи», которым снимается сигнал «строб записи». Так же как и при вводе информации, в этом режиме возможна работа с установкой запроса прерывания, триггером разрешения прерывания для группы А является 6 разряд, а для группы В - 2 разряд порта С. Если прерывание разрешено, то сигналом «строб записи» триггер запроса прерывания (разряд С0 для группы В СЗ - для группы А) будет установлен в состояние 1. При этом на соответствующем входе процессора появится сигнал, прерывающий текущую работу процессора, сброс триггера запроса прерывания осуществляется сигналом «запись», когда очередной байт информации записывается в буферный регистр порта. Незадейетвованные в этом режиме 4 и 5 разряды порта С могут быть использованы по усмотрению разработчика системы.

Функциональная схема адаптера при настройке на вывод:

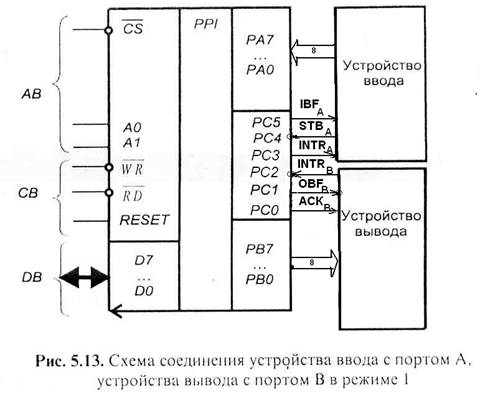

Пример схемы соединения устройства ввода с портом А, устройства вывода с портом В в режиме 1 показано на рис. 5.13.

Ввод данных в режиме 1 осуществляется по каналу А, а управляющие сигналы передаются по линиям РС4 и РС5. Устройство ввода выдает строб приема STB, который указывает на готовность к вводу информации. Этот строб поступает на вход разрешения прерывания от канала А – РС4. Выходной сигнал IBF линии РС5 используется для подтверждения приема. Он формируется по спаду STB и сообщает устройству ввода об окончании приема данных.

Также программируемый параллельный интерфейс формирует также сигнал запроса прерывания INTR, который информирует МП о завершении приема информации. При обмене по прерыванию этот сигнал используется в качестве запроса прерывания, а при программном обмене может игнорироваться. Высокий уровень этого сигнала устанавливается, если STB=1, IBF=1. Нулевой уровень сигнала INTR устанавливается при поступлении сигнала STB при чтении соответствующего порта программируемого параллельного интерфейса.

Для вывода данных в этом режиме используются такие управляющие сигналы: OBF – выходной сигнал, который формируется по фронту WR и сообщает УВВ о готовности к выводу; ACK – входной сигнал, который подтверждает прием информации от БИС интерфейса; INTR – выходной сигнал БИС, сообщающий МП о завершении вывода. Сигнал INTR устанавливается в единицу при OBF=1 и ACK=1, и сбрасывается в нуль сигналом IOW при записи данных в параллельный интерфейс.

Разряды РС6, РС7 при вводе и РС5, РС4 при выводе не участвуют в управлении обменом и могут быть запрограммированы на простой ввод или вывод. Ввод осуществляется чтением порта С, а вывод – записью управляющих слов установки/сброса отдельных разрядов.

Стробированный обмен может осуществляться по прерыванию или по программе. При обмене по прерыванию сигнал INTR поступает в систему прерывания и инициирует обмен. При программном обмене готовность портов А и В определяется путем опроса разрядов INTR A или В соответственно.

Режим 2

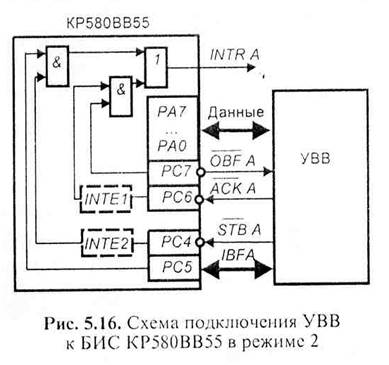

Режим 2 используется для работы с внешними устройствами, имеющими двунаправленную шину данных. Двунаправленный обмен информацией может быть организован только через порт А.

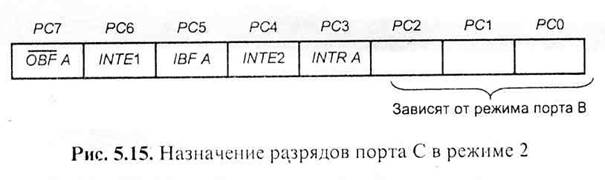

Под управляющие сигналы используются разряды РСЗ-РС7 порта С. Порт В и разряды РС0-РС2 в этом случае могут быть запрограммированы для работы в режиме 0 или 1.

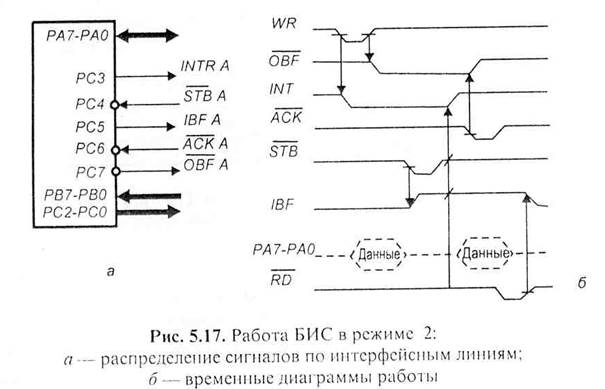

Назначение разрядов порта С в режиме 2 приведено на рис. 5.15.

|

Функциональная схема адаптера в режиме 2 приведена на рис.6.

Вывод БИС INTR A используют как запрос прерывания, как при вводе, так и при выводе информации. Распределение сигналов по интерфейсным линиям и временные диаграммы работы иллюстрирует рис. 5.17.

Программа двунаправленного ввода/вывода по стробу готовности должна сначала обнаружить готовность порта к вводу или выводу по единичному состоянию сигнала INTR A (линия РС3), а потом установить, какие именно данные готовы - для ввода (единичное состояние линии РС4) или вывода (единичное состояние линии РС6). После этого можно осуществлять обмен данными.

Дата публикования: 2015-07-22; Прочитано: 1118 | Нарушение авторского права страницы | Мы поможем в написании вашей работы!