|

Главная Случайная страница Контакты | Мы поможем в написании вашей работы! | |

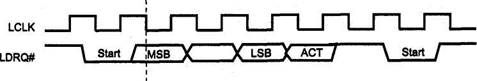

Интерфейс LPC. Рис. 6.17.Посылка запроса DMA или прямого управления

|

|

Рис. 6.17. Посылка запроса DMA или прямого управления

| А | START | CYCTYPE | CHANNEL | SIZE | DATA | TAR | ,ЈSYNC | TAR | |

| б | START | CYCTYPE | CHANNEL | SIZE | TAR | SYNC | DATA | TAR |

Рис. 6.18. Обращения DMA: a — чтение памяти, б — запись в память

Циклы чтения памяти, в зависимости от длины обращения (1, 2 или 4 байта), без тактов ожидания (они скрыты контроллером DMA) занимают 11,18 и 32 тактов (0,33, 0,54 или 0,96 икс), что обеспечивает производительность 3,03, 3,70 или 4,17 Мбайт/с соответственно. Циклы записи занимают 11,14 или 20 тактов (0,33, 0,42 или 0,60 мкс), что обеспечивает производительность 3,03,4,76 или 6,67 Мбайт/с. На рисунке выделены рамкой последовательности полей, повторяющиеся при передаче 2 и 4 байтов.

Прямое управление шиной ведущее устройство запрашивает так же, как и прямой доступ, но указывая зарезервированный номер канала 4 (100). Предоставляя управление, хост в поле START задает номер мастера, который позже определит тип цикла (рис. 6.19). Прямое управление подразумевает обращение к ресурсам хоста (системной памяти, устройству PCI). Данные в 2- и 4-байтных передачах следуют друг за другом без зазора, но в циклах чтения памяти и портов всегда будут такты ожидания, поскольку потребуется время на арбитраж шины PCI или доступ к контроллеру памяти. Из расчета 6 тактов (меньше — вряд ли, возможно и больше) поля SYNC, циклы обращения к памяти (и чтения, и записи) потребуют 25,27 или 31 такт (0,75, 0,81 или 0,93 мкс), что обеспечивает производительность 1,33, 2,47 или 4,30 Мбайт/с. За счет более короткой адресации обращение к портам быстрее — 21, 23 или 27 тактов (0,63, 0,69 или 0,81 мкс), что обеспечивает производительность 1,59, 2,90 или 4,94 Мбайт/с.

| а | START | TAR | CYCTYPE | ADDR | SIZE | TAR | SYNC | DATA | TAR |

| б | START | TAR | CYCTYPE | ADDR | SIZE. | DATA | TAR | SYNC | TAR |

Рис. 6.19. Обращения периферийного устройства (Bus Master): a — чтение памяти или порта,

б — запись в память (порт)

Электрический интерфейс для сигналов LAD[3:0], LFRAME#, LDRQ# и SERIRQ соответствует спецификации PCI 2.1 для питания 3,3 В. Остальные сигналы в зависимости от системной платы могут быть с уровнями как 5 В, так и 3,3 В.

228____________________________________ Глава 6. Шины и карты расширения

Конфигурирование устройств LPC не предусматривает использования протоколов PCI или ISA PnP, поскольку все устройства LPC априорно известны системной BIOS. Для обращения к устройствам LPC хост должен декодировать их адреса и направлять обращения по ним на контроллер LPC.

Дата публикования: 2015-07-22; Прочитано: 366 | Нарушение авторского права страницы | Мы поможем в написании вашей работы!