|

Главная Случайная страница Контакты | Мы поможем в написании вашей работы! | |

Логические элементы КМОП

|

|

Логические элементы на КМОП. Комплементарные (дополняющие) схемы КМОП получили широкое распространение и вытесняют другие типы логических элементов благодаря исключительно малому потреблению мощности при высокой нагрузочной способности и помехоустойчивости.

В основе этих схем лежит инвертор (рисунок 8.1). В качестве VT 1 и VT 2 использованы соответственно n - и p -канальные транзисторы с индуцированным затвором.

|

|

Рис. 8.12. ЛЭ НЕ на КМОП

Пусть в исходном состоянии U вх= 0. Тогда U зи1 = - Е С, значит,

n -канальный транзистор VT 1 – закрыт (он открывается при положительном напряжении на затворе, большим порогового) его выходное напряжение U вых1 ≈ E C, а транзистор VT 2 открыт (поскольку на его затворе отрицательное напряжение, большее порогового). Выходное напряжение высокое. Ток в выходной цепи маленький (несколько нА), определяется закрытым транзистором VT 1.

Если появляется напряжение U зи1 > U ПОР, то U зи2≈0. Транзистор VT 1 открывается, а транзистор VT 2 закрывается, напряжение на выходе низкое (U ВЫХ0 - логический нуль). Ток через структуру попрежнему низкий и равен токам утечки, то есть в статическом режиме мощность почти не потребляется.

Эта особенность является очень важной, поскольку определяет очень малое потребление энергии в КМОП структурах. Суммарная мощность, потребляемая схемой, в основном определяется энергией, которая расходуется на перезаряд паразитных емкостей во время переключения из одного состояния в другое. Паразитные емкости определяются входами других логических элементов, подключенных к выходу данной схемы. Остаточное напряжение на открытом транзисторе очень мало и равно нескольким мкВ (U 0 ≈ 0).

Нагрузочная способность высока, поскольку во входных цепях схемы протекает малый ток и ограничивается только быстродействием, так как надо перезаряжать суммарную паразитную емкость. Коэффициент разветвления по выходу N =20  30.

30.

Помехоустойчивость схем на КМОП выше, чем ТТЛ.

Uпом = (2  3) В. Этому способствует то, что разница между U 1 и U 0 высока. Схема КМОП элемента (К1ЛБ722), реализующая логическую операцию 2И-НЕ представлена на рисунке 8.11.

3) В. Этому способствует то, что разница между U 1 и U 0 высока. Схема КМОП элемента (К1ЛБ722), реализующая логическую операцию 2И-НЕ представлена на рисунке 8.11.

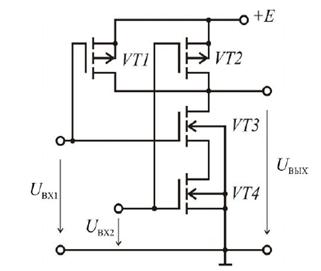

Транзисторы VT 1 и VT 2 с каналом p -типа соединены параллельно, а n -канальные транзисторы VT 3 и VT 4 – последовательно. Подложки и истоки VT 1 и VT 2 соединены с положительным зажимом источника

питания, поэтому

Рис. 8.13. Логическая ИС К1ЛБ722

Пусть на обоих в ходах действует напряжение низкого уровня

U ВХ1 = U ВХ2=0. Поскольку U зи3 = U зи4 =0 транзисторы VT 3 и VT 4 закрыты; U зи1 = U зи2 = - Е и транзисторы VT 1 и VT 2 открыты. Выходное напряжение U вых ≈ Е.

Если U ВХ1 = U ВХ2 ≈ Е. Теперь U зи1 = U зи2 =0 и транзисторы VT 1 и VT 2 закрыты, а транзисторы VT 3 и VT 4 открыты; U вых≈ 0.

Дата публикования: 2014-10-19; Прочитано: 1168 | Нарушение авторского права страницы | Мы поможем в написании вашей работы!